# Parallel Algorithms and Architectures for Low Power Video Decoding MASSACHUSETTS OF TECHNOLOGICAL TOP TO THE POWER TO TH

by

### Vivienne Sze

B.A.Sc. in Electrical Engineering, University of Toronto, 2004 S.M. in Electrical Engineering, Massachusetts Institute of Technology, 2006

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

**ARCHIVES**

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2010

© Massachusetts Institute of Technology 2010. All rights reserved.

| Author                 |                            |            | <del>.</del> |

|------------------------|----------------------------|------------|--------------|

| Department of I        | Electrical Engineering and | d Compute  | er Science   |

|                        |                            | •          | 21, 2010     |

|                        | 4                          | •          |              |

| Certified by           |                            |            |              |

|                        | Anantl                     | ha P. Chan | drakasan     |

| Joseph F. and Nancy P. | Keithley Professor of Ele  |            | •            |

|                        |                            | Thesis S   | upervisor    |

|                        |                            |            | 15           |

| Accepted by            |                            |            |              |

|                        |                            | Terry P.   | Orlando      |

| Chairman, De           | epartment Committee on     | . Graduate | Students     |

# Parallel Algorithms and Architectures for Low Power Video Decoding

by

#### Vivienne Sze

Submitted to the Department of Electrical Engineering and Computer Science on May 21, 2010, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

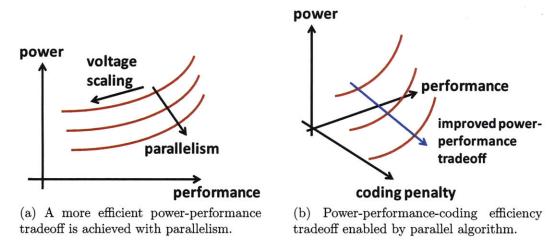

Parallelism coupled with voltage scaling is an effective approach to achieve high processing performance with low power consumption. This thesis presents parallel architectures and algorithms designed to deliver the power and performance required for current and next generation video coding. Coding efficiency, area cost and scalability are also addressed.

First, a low power video decoder is presented for the current state-of-the-art video coding standard H.264/AVC. Parallel architectures are used along with voltage scaling to deliver high definition (HD) decoding at low power levels. Additional architectural optimizations such as reducing memory accesses and multiple frequency/voltage domains are also described. An H.264/AVC Baseline decoder test chip was fabricated in 65-nm CMOS. It can operate at 0.7 V for HD (720p, 30 fps) video decoding and with a measured power of 1.8 mW. The highly scalable decoder can tradeoff power and performance across >100x range.

Second, this thesis demonstrates how serial algorithms, such as Context-based Adaptive Binary Arithmetic Coding (CABAC), can be redesigned for parallel architectures to enable high throughput with low coding efficiency cost. A parallel algorithm called the Massively Parallel CABAC (MP-CABAC) is presented that uses syntax element partitions and interleaved entropy slices to achieve better throughput-coding efficiency and throughput-area tradeoffs than H.264/AVC. The parallel algorithm also improves scalability by providing a third dimension to tradeoff coding efficiency for power and performance.

Finally, joint algorithm-architecture optimizations are used to increase performance and reduce area with almost no coding penalty. The MP-CABAC is mapped to a highly parallel architecture with 80 parallel engines, which together delivers >10x higher throughput than existing H.264/AVC CABAC implementations. A MP-CABAC test chip was fabricated in 65-nm CMOS to demonstrate the power-performance-coding efficiency tradeoff.

Thesis Supervisor: Anantha P. Chandrakasan

Title: Joseph F. and Nancy P. Keithley Professor of Electrical Engineering

.

### Acknowledgments

First, I would like to thank Professor Anantha Chandrakasan for his guidance and mentorship throughout the past six years. I greatly appreciate the opportunities that you have created for me and the exposure you have given me through industry interactions. Thank you for being a strong advocate of my work and always keeping my best interest in mind. I am grateful that you always made yourself available for discussion and advice despite your busy schedule - I've very much enjoyed our talks in the lab and at the Z. It has truly been a rewarding experience to work in the collaborative environment that you have fostered in your lab. Finally, thank you for pioneering the use of voltage scaling with parallelism, which set the foundation for the work presented in this thesis (as well as my masters thesis).

I would like to acknowledge Professor Vivek Goyal and Dr. Madhukar Budagavi for serving on my thesis committee and providing invaluable research advice. I'd also like to extend my thanks to Vivek for serving on my RQE committee. Much of what I learned about video coding came from the many engaging discussions I had with Madhukar during my summers at Texas Instruments (TI). I look forward to many more in the future.

I'd like to thank Dennis Buss and Alice Wang for their help in making the test chips featured in this thesis possible - especially with surprises we faced with the last one. I'd also like to thank Alice for the many highlights (IV REAL!) during my time in Dallas. Thanks to Minhua Zhou, Bruce Flinchbaugh and Martin Izzard for providing me the opportunity to do several internships at TI, where I ramped up on video and got to experience R & D in an industry setting. I'd also like to thank Minhua and Umut Demircin for technical discussions.

I'd like to thank Professor Peter Ottensmeyer for giving me the opportunity to work in his lab over a decade ago, where I got my first taste of research. He taught me how to take a complex and seemingly insurmountable problem, and break it into smaller more manageable parts.

My time at MIT was truly enriched by the people I interacted with on a daily basis. Thanks to the past and present members of ananthagroup for making the lab an incredibly enjoyable and interesting place to work, and for the many friendships and laughs. For all the

hours we spend in the lab, I'm glad it's with you folks. I had great fun collaborating with Daniel Finchelstein and Mahmut Ersin Sinangil on the video decoder chip. Thanks to Yogesh Ramadass for helping us fix those 1000+ antenna violations two days before tapeout. I'd like to thank Raul Blazquez for his continued mentorship post-graduation; Manish Bhardwaj for his insight on all things technical and non-technical; Joyce Kwong for discussions on all things digital; and Nathan Ickes for coming to the rescue during soldering mishaps and answering all my PCB and FPGA related questions. To Fred (Chen and Lee), Brian Ginsburg, Raul, Alice, Manish, and Daniel thanks for all your career advice and for answering my many questions during the whole job hunting hoopla. I'd like to thank Alex, Ben, Brian, Daniel, Dave, Denis, Fred, Joyce, Mahmut, Manish, Marcus, Masood, Nathan, Naveen, Pat, Payam, Phil, Raul, and Yogesh, among others for the great lunchtime conversation that often provided a nice break from research. I'd like to thank Joyce, Denis, Raul and Bonnie for taking the time to proof-read various portions of this thesis and providing valuable feedback.

Thanks to Margaret Flaherty for her help with logistics ranging from rushed purchase orders, to scheduling appointments, to finding a room for the defense. Thanks to Danielle Guichard-Ashbrook for always being incredibly patient and helpful during my many visits to the ISO. I'd also like to thank the MTL Compute Team for their quick response whenever the computers or tools when down or a file needed to be recovered.

Finally, I'd like to thank those who provided invaluable support outside the lab. To my SATC gals, thanks for the brunches, trips, and memories. Joyce, thanks for being great buddy both in and out of the lab. Rumi Chunara, thanks for keeping me in shape on our morning runs and swims. Maryam Modir Shanechi, I couldn't have asked for a better friend and roommate. Thanks for being my family in Boston throughout the past six years. And to my family in Toronto, Mom, Jen and TeeTee, thank you for your support and encouragement throughout this journey. Your unconditional love and support mean the world to me.

Done and done!

This work was funded by Texas Instruments, who also provided fabrication services, and in part by an Natural Sciences and Engineering Research Council of Canada (NSERC) Fellowship.

# Contents

| 1 | Intr | oducti | on                                          | 21 |

|---|------|--------|---------------------------------------------|----|

|   | 1.1  | Next ( | Generation Video Coding                     | 22 |

|   | 1.2  | Enabli | ing Parallelism                             | 24 |

|   | 1.3  | Voltag | ge Scaling                                  | 26 |

|   | 1.4  | Scalab | oility                                      | 28 |

|   | 1.5  | Thesis | Contributions                               | 30 |

| 2 | Low  | Powe   | er Architecture for H.264/AVC Video Decoder | 35 |

|   | 2.1  | Overv  | iew of Video Coding Standard H.264/AVC      | 35 |

|   |      | 2.1.1  | Partitioning the Video Sequence             | 37 |

|   |      | 2.1.2  | Prediction                                  | 37 |

|   |      | 2.1.3  | Transform and Quantization                  | 38 |

|   |      | 2.1.4  | Entropy Coding                              | 39 |

|   |      | 2.1.5  | Deblocking                                  | 39 |

|   |      | 2.1.6  | GOP and Prediction Structure                | 40 |

|   |      | 2.1.7  | Profiles and Levels                         | 40 |

|   | 2.2  | Relate | ed Work                                     | 42 |

|   | 2.3  | Decod  | ler Pipeline Architecture                   | 42 |

|   | 2.4  | Parall | elism                                       | 45 |

|   |      | 2.4.1  | Motion Compensation (MC)                    | 45 |

|   |      | 2.4.2  | Deblocking Filter (DB)                      | 47 |

|   | 2.5  | Multip | ole Voltage/Frequency Domains                 | 51           |

|---|------|--------|-----------------------------------------------|--------------|

|   | 2.6  | Dynar  | nic Voltage and Frequency Scaling (DVFS)      | 52           |

|   | 2.7  | Memo   | ry Optimization                               | 56           |

|   |      | 2.7.1  | On Chip Caching                               | 57           |

|   |      | 2.7.2  | Reducing MC Redundant Reads                   | 58           |

|   | 2.8  | Test S | etup                                          | 59           |

|   | 2.9  | Result | s and Measurements                            | 62           |

|   |      | 2.9.1  | Power Breakdown and Switching Activity        | 65           |

|   |      | 2.9.2  | Area Breakdown                                | 68           |

|   |      | 2.9.3  | System Level Issues                           | 69           |

|   | 2.10 | Summ   | ary and Conclusions                           | 69           |

| 3 | Mag  | oivolv | Danellal CADAC Almonithms                     | <b>27</b> -1 |

| 3 | 3.1  |        | Parallel CABAC Algorithm                      | 71           |

|   | 3.1  |        | iew of CABAC                                  | 71           |

|   |      | 3.1.1  | Entropy Coding                                | 72           |

|   |      | 3.1.2  | Binarization                                  | 72           |

|   |      | 3.1.3  | Binary Arithmetic Coding                      | 74           |

|   |      | 3.1.4  | Probability (Context) Modeling and Estimation | 75           |

|   |      | 3.1.5  | CABAC Example                                 | 77           |

|   |      | 3.1.6  | Performance Requirements                      | 81           |

|   | 3.2  | Relate | d Work                                        | 82           |

|   |      | 3.2.1  | Frame Workload Averaging (Buffering)          | 82           |

|   |      | 3.2.2  | Bin Parallel Processing                       | 82           |

|   |      | 3.2.3  | Frame and/or Slice Parallel Processing        | 83           |

|   |      | 3.2.4  | Entropy Slices                                | 84           |

|   | 3.3  | Massiv | rely Parallel CABAC (MP-CABAC)                | 86           |

|   |      | 3.3.1  | Improving Tradeoffs                           | 86           |

|   |      | 3.3.2  | Syntax Element Partitions (SEP)               | 86           |

|   |      | 3.3.3  | Interleaved Entropy Slices (IES)              | 95           |

|   | 3.4 | Standardization Effort                      | 2 |

|---|-----|---------------------------------------------|---|

|   | 3.5 | Summary and Conclusions                     | 4 |

| 4 | Arc | chitecture of Massively Parallel CABAC 10   | 7 |

|   | 4.1 | Data Structure                              | 7 |

|   | 4.2 | CABAC Engine                                | 9 |

|   |     | 4.2.1 Context Selection                     | 2 |

|   |     | 4.2.2 Binary Arithmetic Decoder             | 6 |

|   | 4.3 | Syntax Element Partitions Processing        | 3 |

|   |     | 4.3.1 Division of the Context Selection FSM | 4 |

|   |     | 4.3.2 Distributed Context Memory            | 6 |

|   |     | 4.3.3 SEP FIFOs                             | 6 |

|   | 4.4 | Interleaved Entropy Slices Processing       | 7 |

|   |     | 4.4.1 IES FIFOs                             | 8 |

|   |     | 4.4.2 Row Balancing                         | 1 |

|   | 4.5 | Simulation Results                          | 1 |

|   |     | 4.5.1 Throughput                            | 2 |

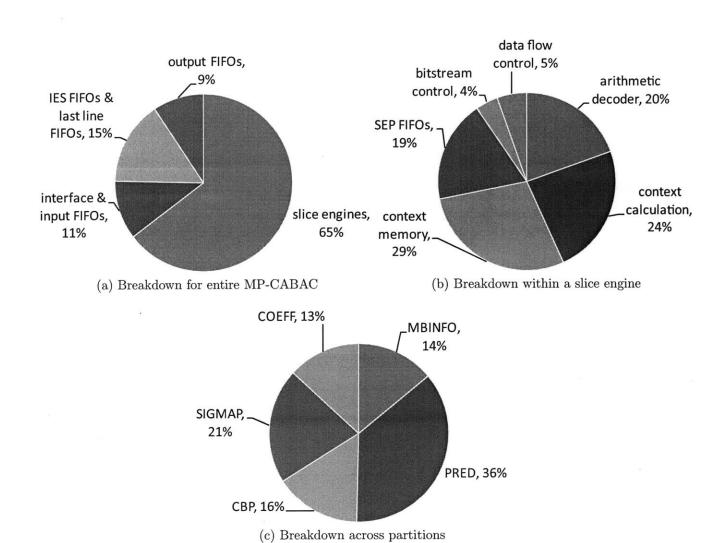

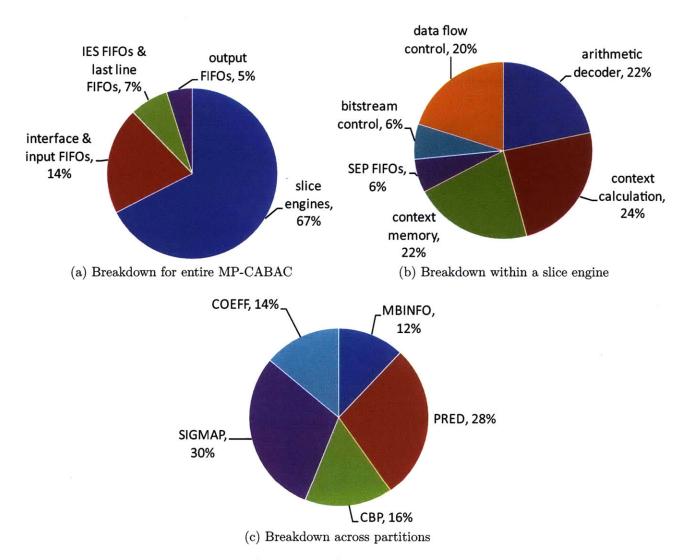

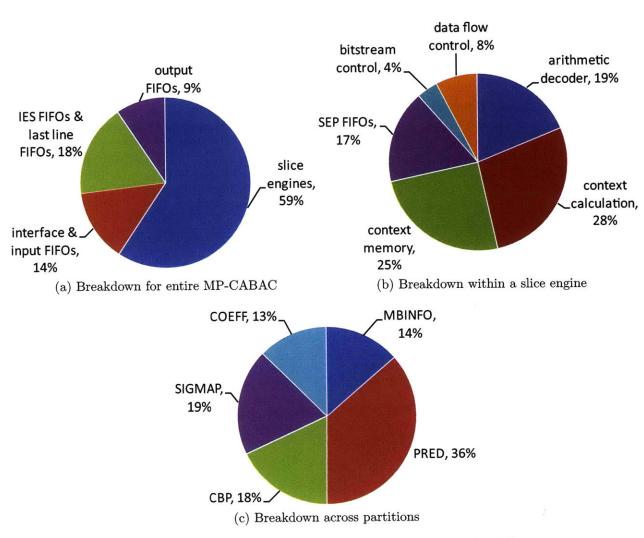

|   |     | 4.5.2 Area Breakdown                        | 5 |

|   |     | 4.5.3 Comparison                            | 7 |

|   | 4.6 | Summary and Conclusions                     | 9 |

| 5 | Mas | ssively Parallel CABAC Test Chip 14         | 1 |

|   | 5.1 | Functionality                               | 1 |

|   | 5.2 | Off-chip Interface                          | 2 |

|   | 5.3 | Bitstream Control                           | 5 |

|   | 5.4 | Configurability                             | 6 |

|   | 5.5 | Global Signals                              | 6 |

|   | 5.6 | Separate Voltage/Frequency Domains          | 6 |

|   | 5.7 | Floorplan                                   | 0 |

|              | 5.8            | Test S   | etup                                      | 151 |

|--------------|----------------|----------|-------------------------------------------|-----|

|              | 5.9            | Result   | s and Measurements                        | 155 |

|              |                | 5.9.1    | Tradeoffs                                 | 157 |

|              |                | 5.9.2    | Power Breakdown and Switching Activity    | 160 |

|              | 5.10           | Summ     | ary                                       | 160 |

| 6            | Con            | clusion  | ns and Future Work                        | 165 |

|              | 6.1            | Summa    | ary of Contributions                      | 166 |

|              |                | 6.1.1    | Parallel Architectures                    | 166 |

|              |                | 6.1.2    | Parallel Algorithms                       | 166 |

|              |                | 6.1.3    | Joint Algorithm/Architecture Optimization | 167 |

|              |                | 6.1.4    | Test Chips                                | 167 |

|              | 6.2            | Future   | Work                                      | 168 |

| $\mathbf{A}$ | $\mathbf{Add}$ | litional | Details on CABAC                          | 171 |

|              | A.1            | Perform  | mance Requirements Calculations           | 171 |

|              | A.2            | Bin Pa   | rallelism for H.264/AVC CABAC             | 172 |

|              | A.3            | Bin Pa   | trallelism for 'H.265' CABAC              | 175 |

|              |                | A.3.1    | Coding Efficiency and Throughput          | 178 |

|              |                | A.3.2    | Area Cost                                 | 178 |

| В            | Calc           | culating | g Coding Efficiency                       | 179 |

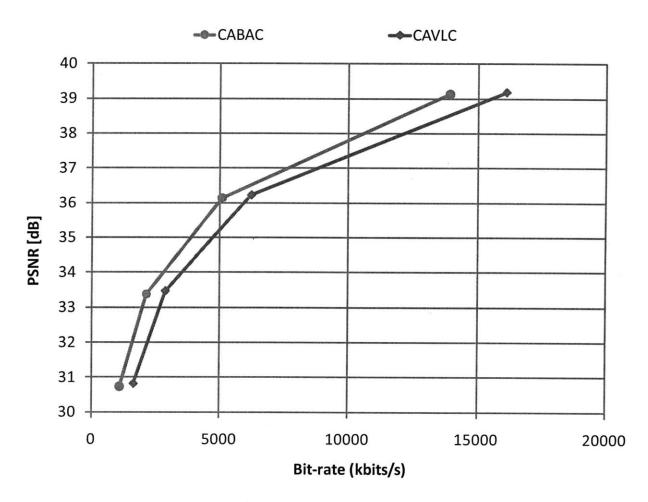

|              | B.1            | CAVLO    | C vs. CABAC for HD                        | 181 |

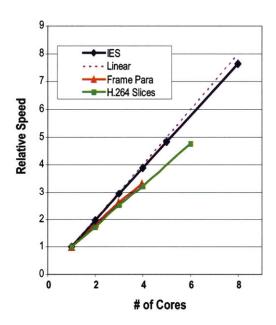

| $\mathbf{C}$ | Ena            | bling N  | Multi-Core Processing with IES            | 183 |

| D            | Con            | tent of  | SEP FIFOs                                 | 187 |

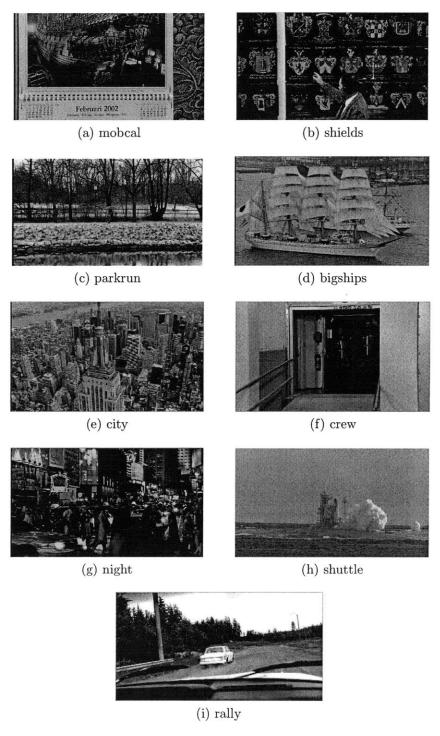

| ${f E}$      | Vide           | eo Test  | Bitstreams                                | 191 |

| F            | Pacl           | raging   | for MP-CABAC                              | 105 |

# List of Figures

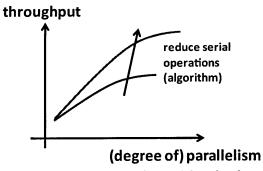

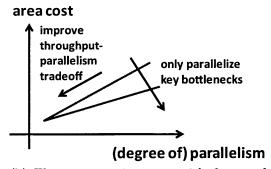

| 1-1  | Relationship between throughput, parallelism and area cost. Increasing the throughput improvement per degree of parallelism (Fig 1-1a) also reduces the area cost (Fig. 1-1b)                       | 25 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

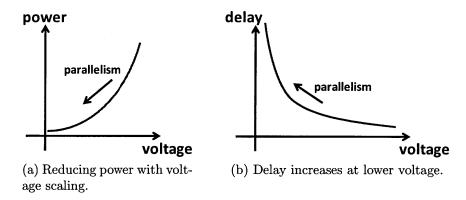

| 1-2  | Relationship between voltage, power and delay. Parallelism can be used to mitigate delay to enable lower voltage and consequently lower power consumption.                                          | 28 |

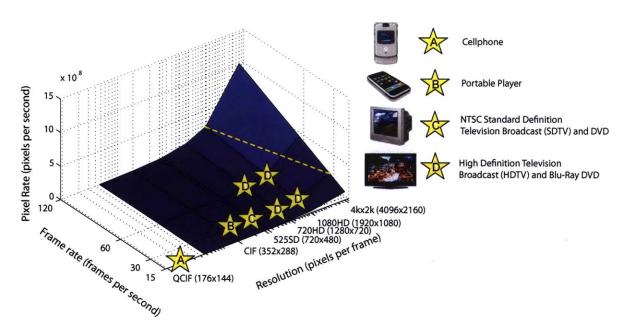

| 1-3  | Performance requirements for various applications based on frame rate and resolution [25]. Yellow dashed line shows limit of H.264/AVC standard. The                                                | 29 |

| 1-4  | Tradeoff enabled with parallel architectures and algorithms                                                                                                                                         | 31 |

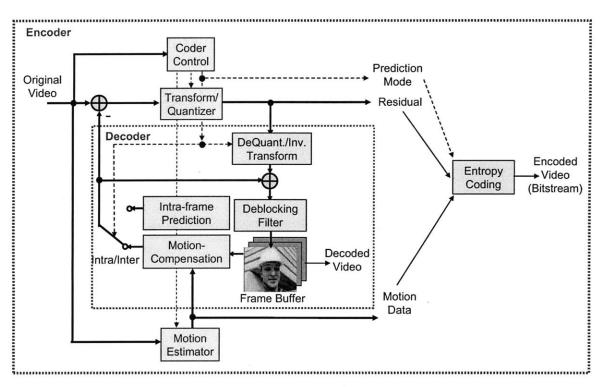

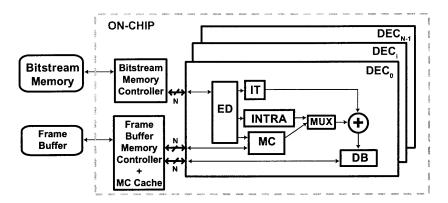

| 2-1  | Basic video coding structure for H.264/AVC, the state-of-the-art video coding standard. Note that the decoder is embedded within the encoder. This figure is adopted from [37].                     | 36 |

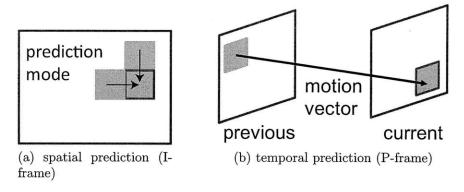

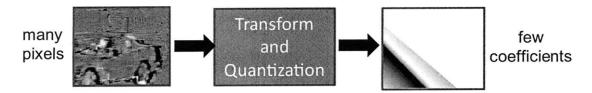

| 2-2  |                                                                                                                                                                                                     | 38 |

| 2-3  | - P                                                                                                                                                                                                 | 39 |

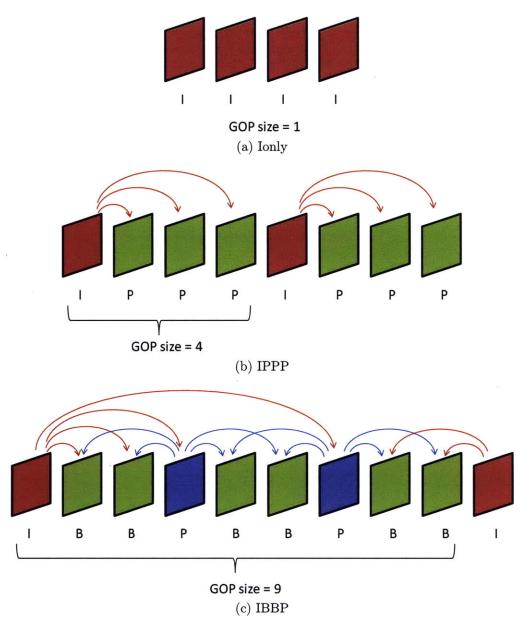

| 2-4  |                                                                                                                                                                                                     | 41 |

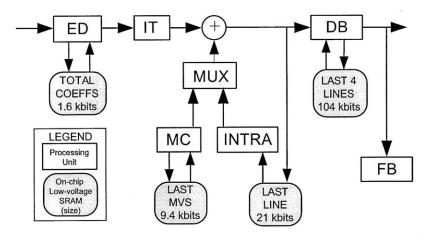

| 2-5  | (                                                                                                                                                                                                   | 43 |

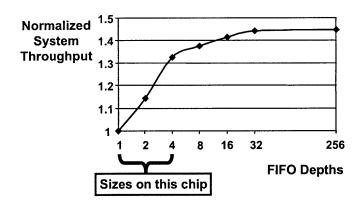

| 2-6  | Longer FIFOs average out workload variations to minimize pipeline stalls.                                                                                                                           | 10 |

| 2-0  | <u> </u>                                                                                                                                                                                            | 45 |

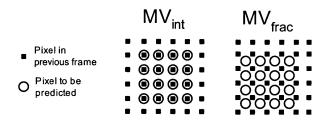

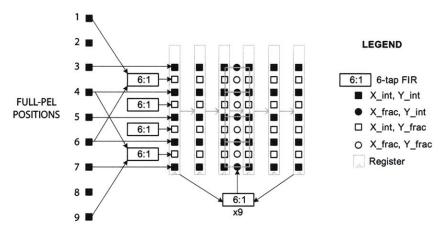

| 2-7  |                                                                                                                                                                                                     | 46 |

| 2-8  | 8                                                                                                                                                                                                   | 47 |

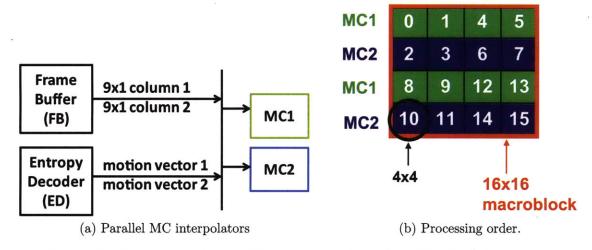

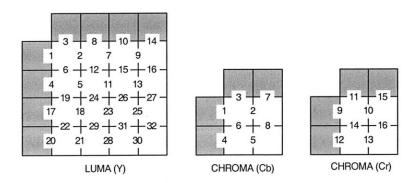

| 2-9  | Parallel motion compensation (MC) interpolators. Note: the numbered 4x4 blocks reflect the processing order within a macroblock defined by the H.264/AVC                                            |    |

|      | standard                                                                                                                                                                                            | 47 |

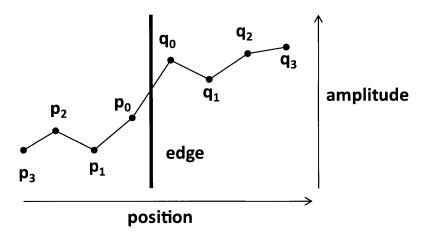

| 2-10 | The four pixels on either side of the edge are used as inputs to the deblocking filter                                                                                                              | 48 |

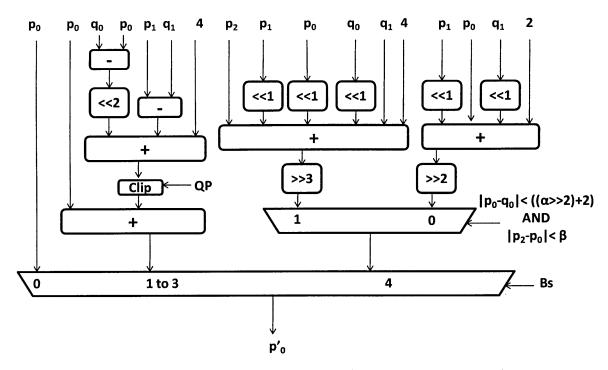

| 2-11 | Architecture of luma filter for pixel $p_0$ ( $q_0$ uses a similar filter). Different filters are used for pixels $p_1$ , $q_1$ , $p_2$ , and $q_2$ . Filters are defined in [26]. Pixels $p_3$ and |    |

|      |                                                                                                                                                                                                     | 49 |

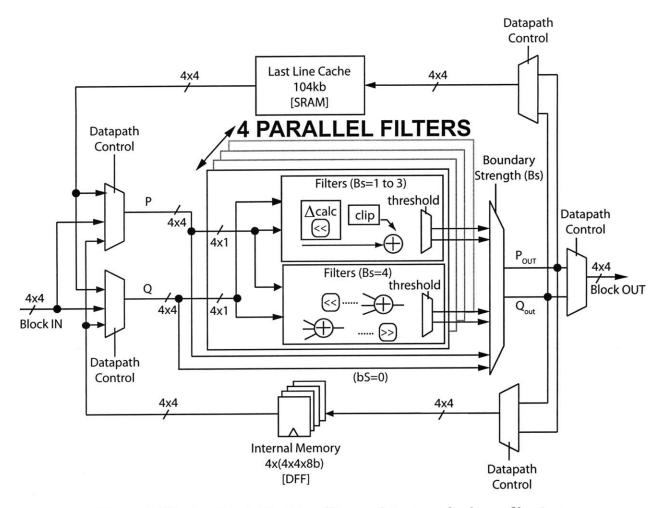

| 2-12 | Parallel deblocking filter architecture for luma filtering                                                                                                                                          | 50 |

| 2-13 | Deblocking edge filtering order.                                                                                                                                                                    | 50 |

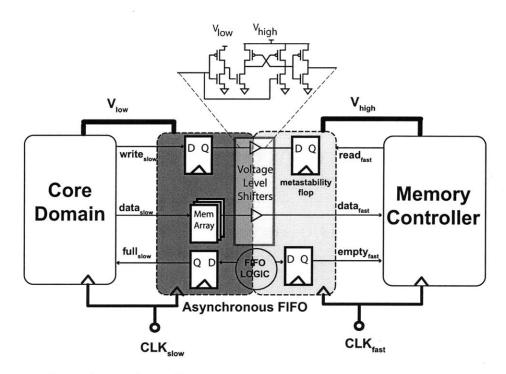

| 2-14                                                 | Independent voltage/frequency domains are separated by asynchronous first-in-first-out queues (FIFOs) and level-converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52                                     |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

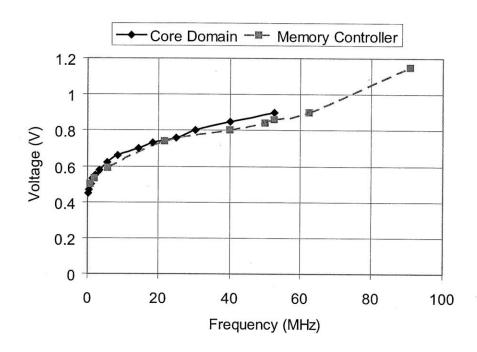

| 2-15                                                 | Measured frequency versus voltage for core domain and memory controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 02                                     |

|                                                      | Use this plot to determine maximum frequency for given voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                                     |

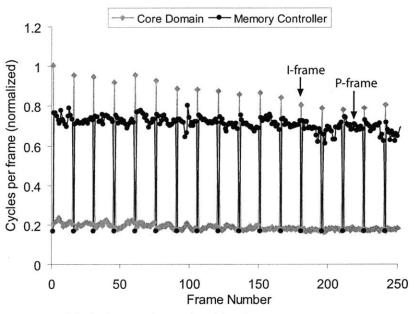

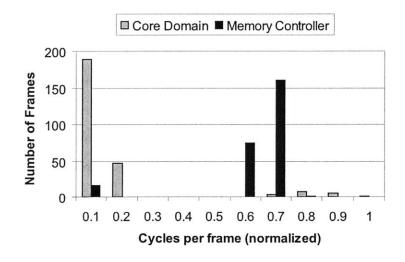

| 2-16                                                 | Workload variation across 250 frames of mobcal sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55                                     |

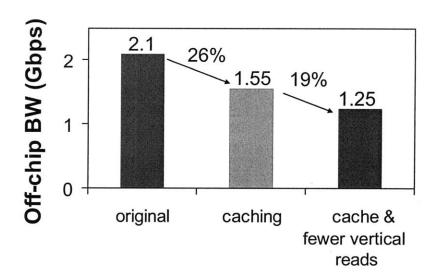

|                                                      | Reduction in overall memory bandwidth from caching and reuse MC data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57                                     |

|                                                      | On-chip caches to reduce off-chip memory bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                     |

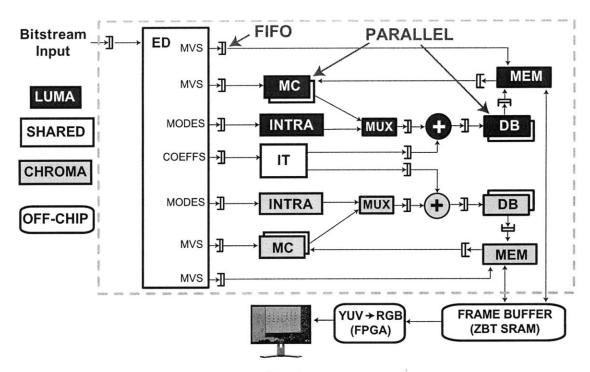

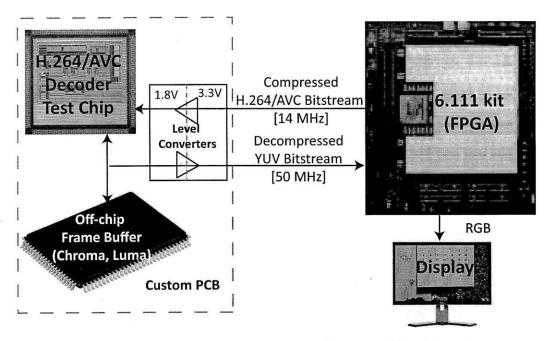

|                                                      | Connections in test setup for H.264/AVC decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60                                     |

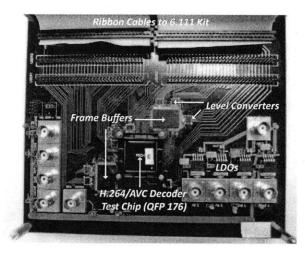

|                                                      | Photo of custom PCB designed to connect the H.264/AVC decoder test chip with the rest of the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                     |

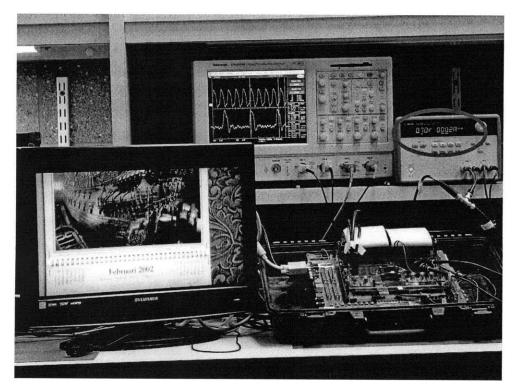

| 2-21                                                 | Photo of real-time system demo. Voltage and current measurements of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| 0.00                                                 | core domain can be seen in the upper right corner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61                                     |

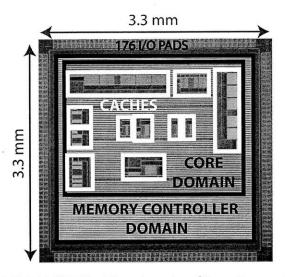

|                                                      | Die photo of H.264/AVC video decoder (domains and caches are highlighted).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                     |

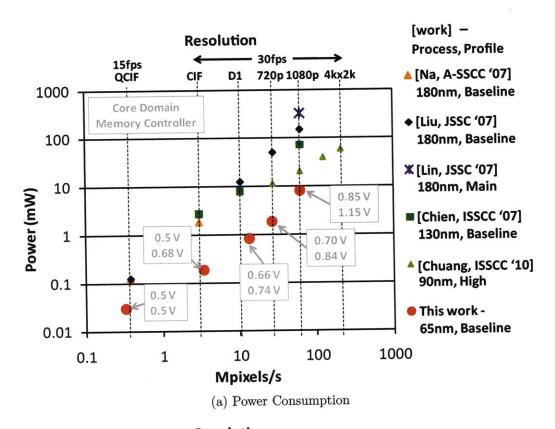

|                                                      | Comparison with other H.264/AVC decoders [38–41,60].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64                                     |

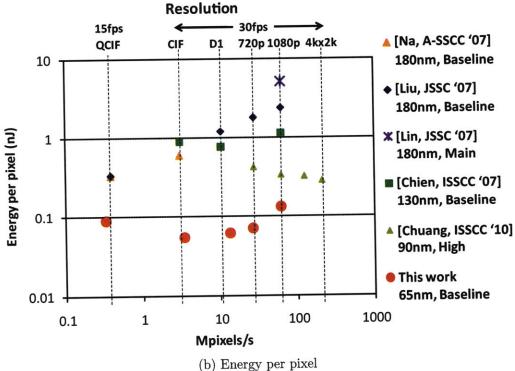

|                                                      | Variation of minimum core voltage supply for 720p decoding across test chips.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65                                     |

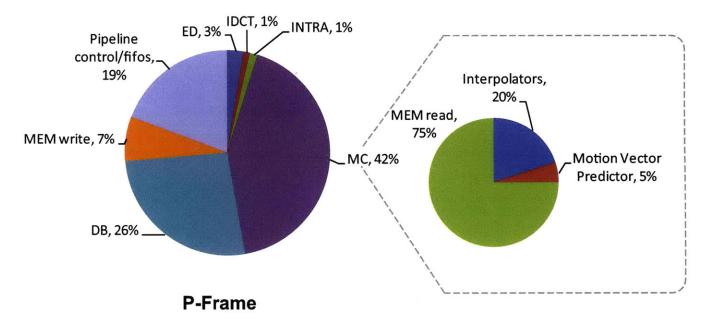

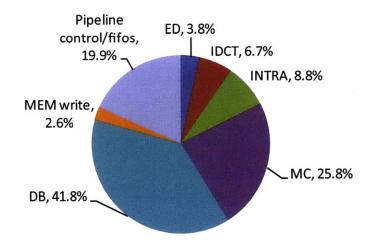

|                                                      | Simulated (post-layout) power breakdown during P-frame decoding Post-layout simulated leakage power breakdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66                                     |

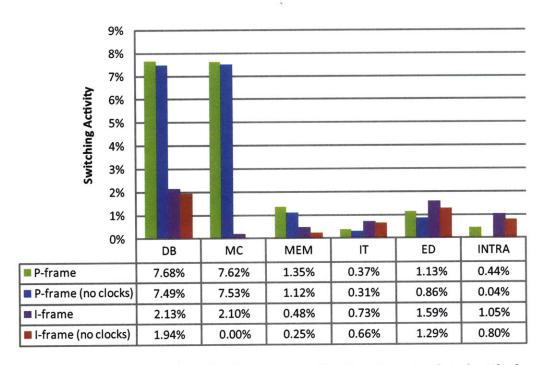

|                                                      | The switching activity of each module in the decoder, simulated with the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66                                     |

| 2-21                                                 | mobcal sequence. Note: these switching activity numbers are for logic only;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

|                                                      | the SRAM caches are not included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 67                                     |

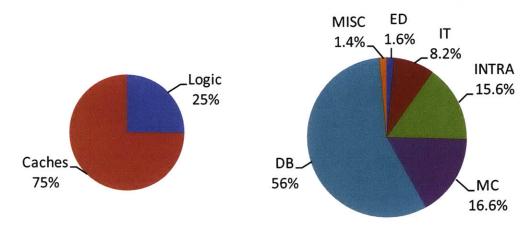

| 2-28                                                 | Post-layout area breakdown (includes logic and memory)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68                                     |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

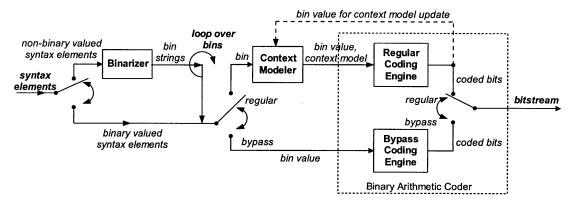

| 3-1                                                  | Block diagram of CABAC encoder [67]. Non-binary syntax elements pass through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|                                                      | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74                                     |

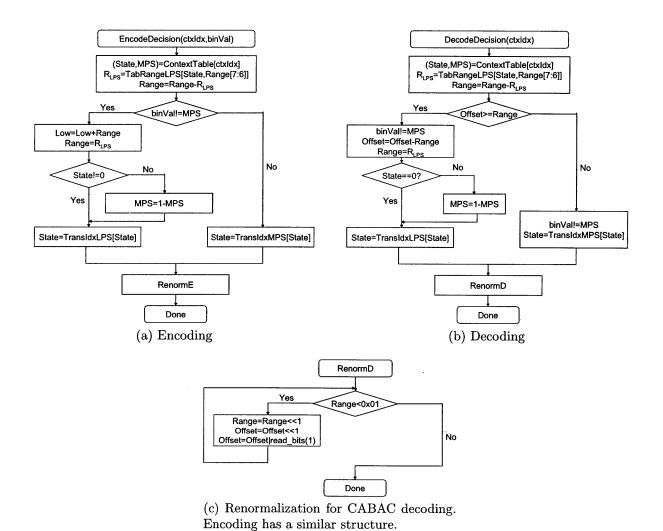

| 3-2                                                  | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76                                     |

| 3-2<br>3-3                                           | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76<br>79                               |

| 3-2<br>3-3<br>3-4                                    | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution Data flow of the arithmetic coding engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76                                     |

| 3-2<br>3-3<br>3-4                                    | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76<br>79                               |

| 3-2<br>3-3                                           | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution Data flow of the arithmetic coding engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76<br>79                               |

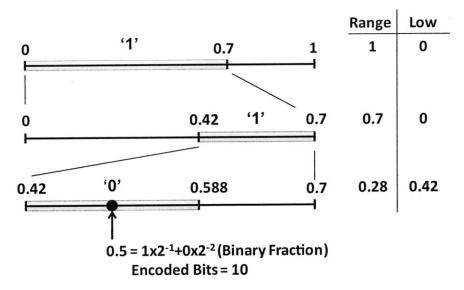

| 3-2<br>3-3<br>3-4                                    | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76<br>79<br>80                         |

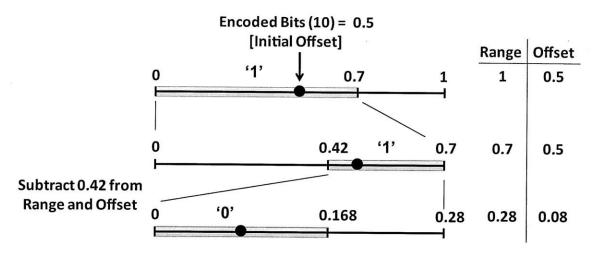

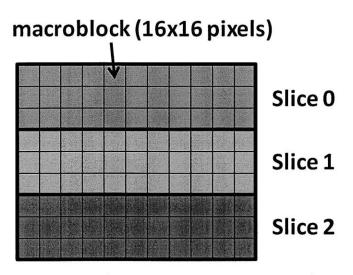

| 3-2<br>3-3<br>3-4                                    | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution.  Data flow of the arithmetic coding engine.  Example of arithmetic coding of sequence '110'.  Example of arithmetic decoding of sequence '110'.  Example of three H.264/AVC slices in a frame. H.264/AVC slices are contiguous groups of macroblocks that can be encoded/decoded independently from each other. This enables parallelism, but reduces coding efficiency since redundancy across slices cannot be leveraged for prediction.                                                                                                                                                                                                                                                                                                                             | 76<br>79                               |

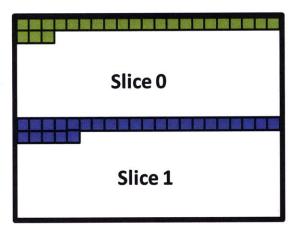

| 3-2<br>3-3<br>3-4<br>3-5                             | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76<br>79<br>80                         |

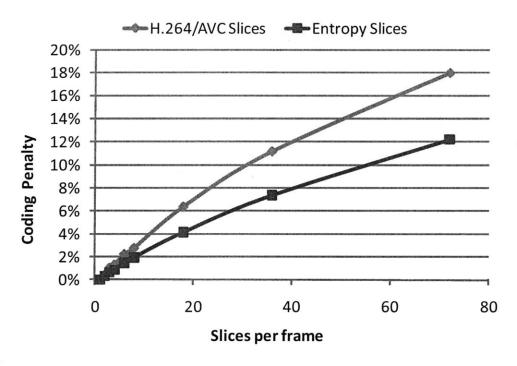

| 3-2<br>3-3<br>3-4<br>3-5                             | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution.  Data flow of the arithmetic coding engine.  Example of arithmetic coding of sequence '110'.  Example of arithmetic decoding of sequence '110'.  Example of three H.264/AVC slices in a frame. H.264/AVC slices are contiguous groups of macroblocks that can be encoded/decoded independently from each other. This enables parallelism, but reduces coding efficiency since redundancy across slices cannot be leveraged for prediction.                                                                                                                                                                                                                                                                                                                             | 76<br>79<br>80<br>84                   |

| 3-2<br>3-3<br>3-4<br>3-5                             | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution.  Data flow of the arithmetic coding engine.  Example of arithmetic coding of sequence '110'.  Example of arithmetic decoding of sequence '110'.  Example of three H.264/AVC slices in a frame. H.264/AVC slices are contiguous groups of macroblocks that can be encoded/decoded independently from each other. This enables parallelism, but reduces coding efficiency since redundancy across slices cannot be leveraged for prediction.  Coding penalty versus slices per frame. Sequence bigships, QP=27, under common conditions [34].                                                                                                                                                                                                                            | 76<br>79<br>80<br>84<br>85             |

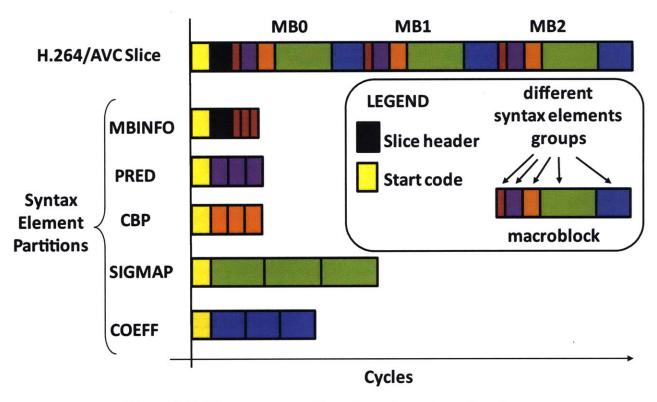

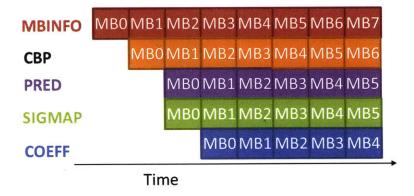

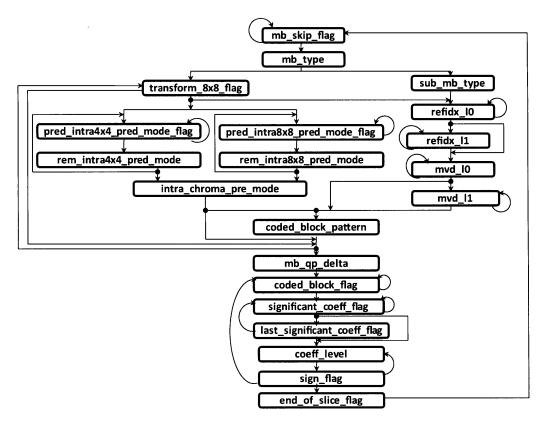

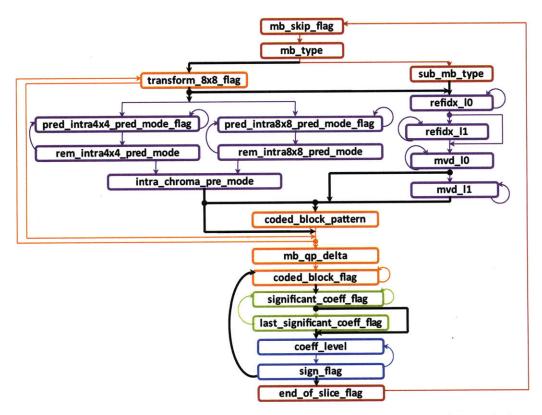

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8        | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution.  Data flow of the arithmetic coding engine.  Example of arithmetic coding of sequence '110'.  Example of arithmetic decoding of sequence '110'.  Example of three H.264/AVC slices in a frame. H.264/AVC slices are contiguous groups of macroblocks that can be encoded/decoded independently from each other. This enables parallelism, but reduces coding efficiency since redundancy across slices cannot be leveraged for prediction.  Coding penalty versus slices per frame. Sequence bigships, QP=27, under common conditions [34].  Concurrency with syntax element partitioning.  Dependencies between syntax element groups.                                                                                                                                | 76<br>79<br>80<br>84<br>85<br>87<br>88 |

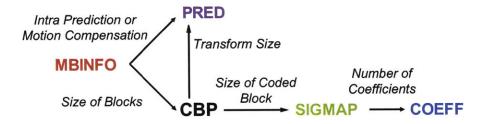

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9 | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution.  Data flow of the arithmetic coding engine.  Example of arithmetic coding of sequence '110'.  Example of arithmetic decoding of sequence '110'.  Example of three H.264/AVC slices in a frame. H.264/AVC slices are contiguous groups of macroblocks that can be encoded/decoded independently from each other. This enables parallelism, but reduces coding efficiency since redundancy across slices cannot be leveraged for prediction.  Coding penalty versus slices per frame. Sequence bigships, QP=27, under common conditions [34].  Concurrency with syntax element partitioning.  Dependencies between syntax element groups.  Partitions are processed in a pipelined manner such that different macroblocks from each partition are processed in parallel. | 76<br>79<br>80<br>84<br>85<br>87       |

| 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8        | through the binarizer to be mapped to binary symbols (bins). The majority of the bins are compressed with two forms of arithmetic coding: bypass and regular. Bypass coding assumes a uniform distribution for bins, while regular coding requires context modeling to estimate the bin distribution.  Data flow of the arithmetic coding engine.  Example of arithmetic coding of sequence '110'.  Example of arithmetic decoding of sequence '110'.  Example of three H.264/AVC slices in a frame. H.264/AVC slices are contiguous groups of macroblocks that can be encoded/decoded independently from each other. This enables parallelism, but reduces coding efficiency since redundancy across slices cannot be leveraged for prediction.  Coding penalty versus slices per frame. Sequence bigships, QP=27, under common conditions [34].  Concurrency with syntax element partitioning.  Dependencies between syntax element groups.  Partitions are processed in a pipelined manner such that different macroblocks from each partition are processed in parallel. | 76<br>79<br>80<br>84<br>85<br>87<br>88 |

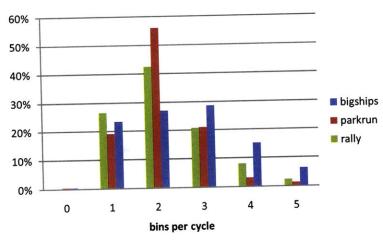

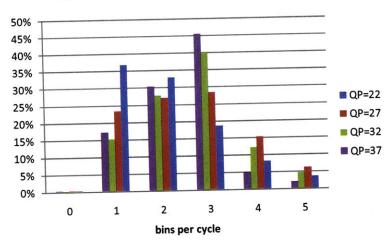

|      | Average bin distribution per frame                                                                                                    | 93  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

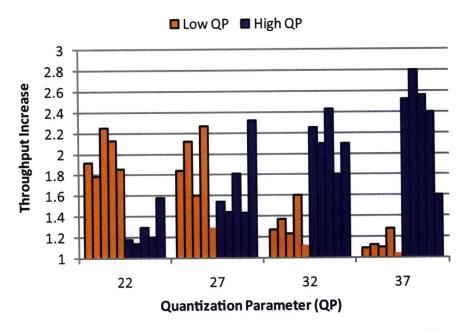

| 3-12 | High QP (blue); Low QP (orange). Sequences (left to right): bigships, city,                                                           |     |

|      | crew, night, and shuttle                                                                                                              | 94  |

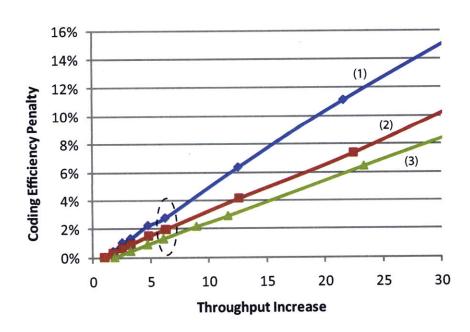

| 3-13 | Coding efficiency vs. throughput for (1) H.264/AVC slices, (2) entropy slices                                                         |     |

|      | and (3) entropy slices with syntax element partitions. Sequence bigships                                                              |     |

|      | (QP=27) [34]                                                                                                                          | 94  |

|      | Macroblock allocation for entropy slices proposed by Sharp and MediaTek                                                               | 96  |

|      | Decoded syntax elements need to be buffered                                                                                           | 96  |

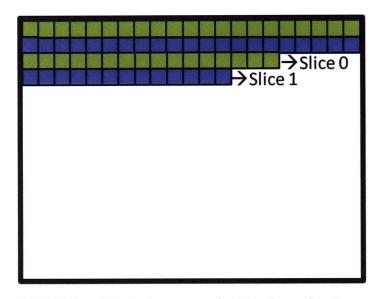

|      | Macroblock allocation for interleaved entropy slices                                                                                  | 96  |

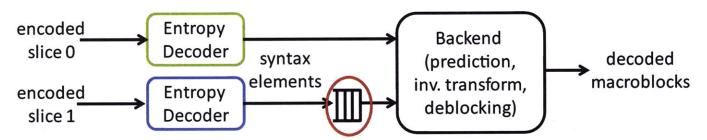

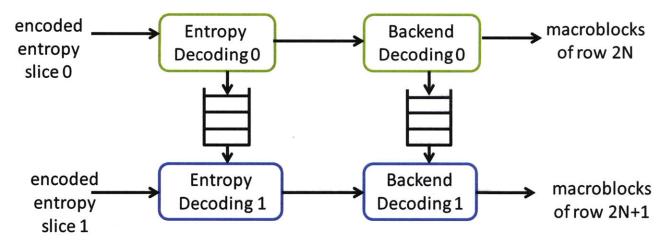

| 3-17 | Interleaved Entropy Slices architecture example for 2x parallel decoding. Note that the <i>entire</i> decode path can be parallelized | 97  |

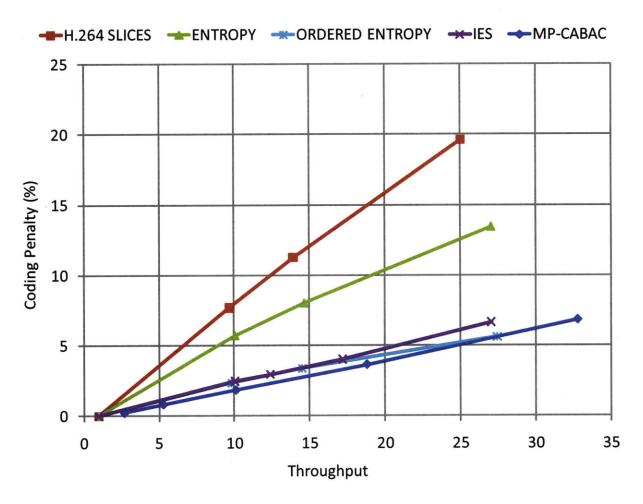

| 9 10 | Tradeoff between coding efficiency and throughput for various parallel CABAC                                                          | 31  |

| 9-10 | approaches. Coding efficiency and throughput are averaged across predic-                                                              |     |

|      | tion structures, sequences and quantization. Note that the area cost versus                                                           |     |

|      | throughput tradeoff for the entropy slices and ordered entropy slices are the                                                         |     |

|      | same since they have the same throughput                                                                                              | 101 |

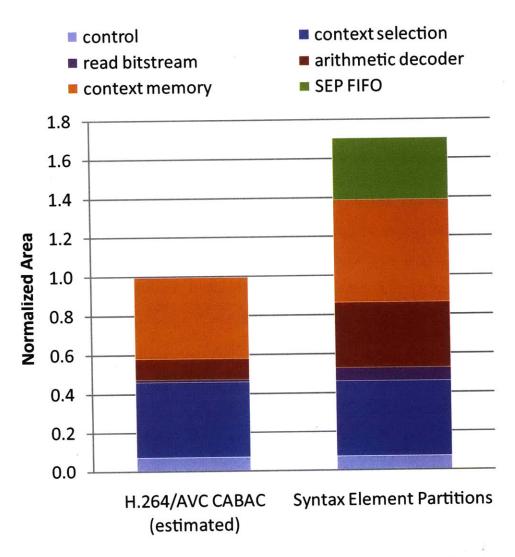

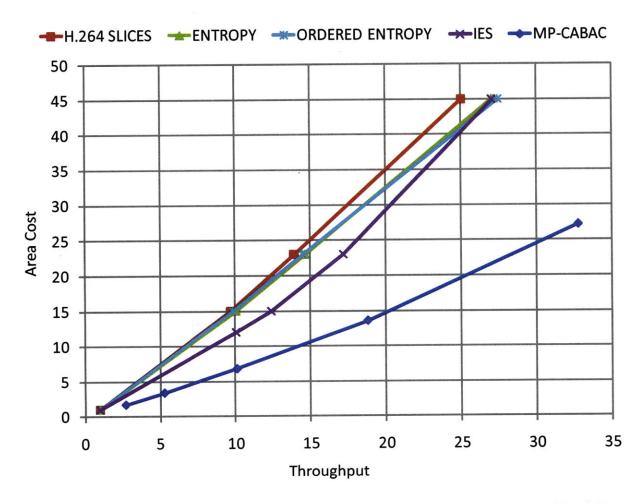

| 3-19 | Area cost versus throughput tradeoff for the various parallel CABAC approaches                                                        |     |

| 0 15 |                                                                                                                                       |     |

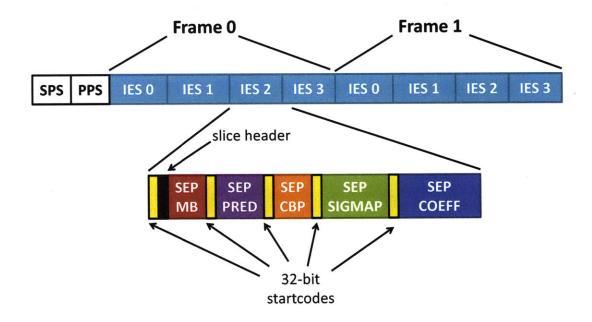

| 4-1  | Data structure of the encoded bitstream with Massively Parallel CABAC                                                                 |     |

|      | (MP-CABAC). In this example, four Interleaved Entropy Slices (IES) are                                                                |     |

|      | used per frame.                                                                                                                       | 108 |

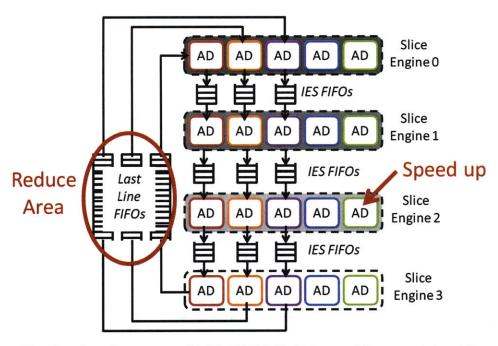

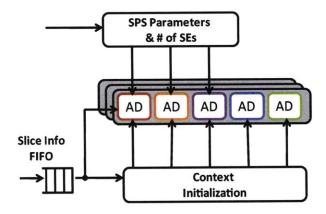

| 4-2  | Top level architecture of MP-CABAC. Joint architecture/algorithm optimiza-                                                            |     |

|      | tions were performed to speed up the AD and reduce the area of the last line                                                          |     |

|      | FIFO                                                                                                                                  | 109 |

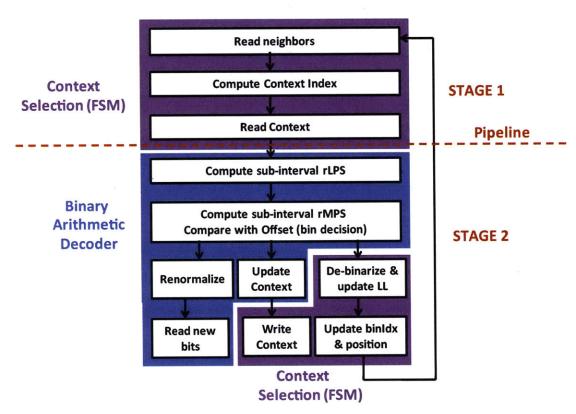

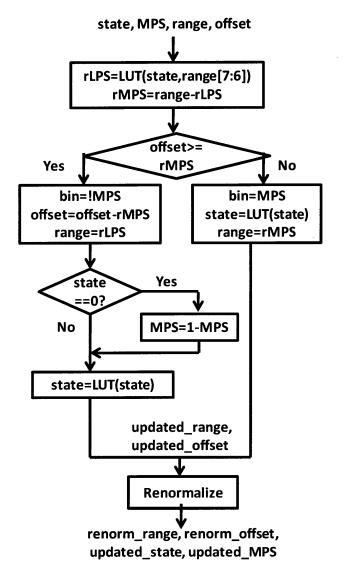

| 4-3  | Main steps in CABAC decoding                                                                                                          | 110 |

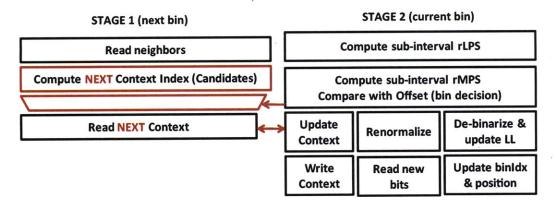

| 4-4  | Pipelining CABAC engine to speed up performance. Connections between                                                                  |     |

|      | the two pipeline stages required due to feedback loop are highlighted in red.                                                         | 113 |

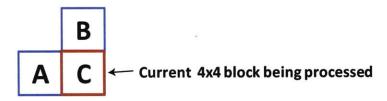

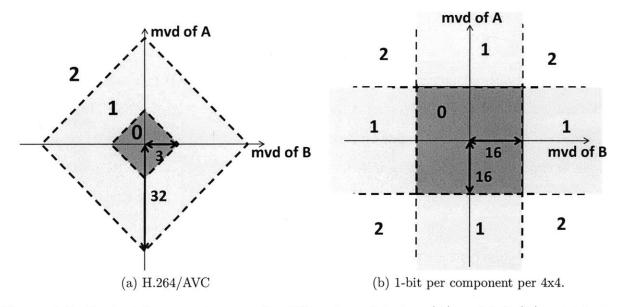

| 4-5  | Last line dependencies for motion vector difference (mvd)                                                                             | 114 |

| 4-6  | Context increments $\chi_{mvd}$ for different mvd in top (A) and left (B) neighboring                                                 |     |

|      | 4x4 blocks                                                                                                                            | 115 |

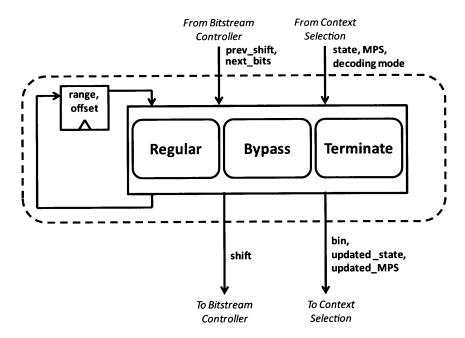

| 4-7  | Architecture of arithmetic decoder with three different decoding mode                                                                 | 117 |

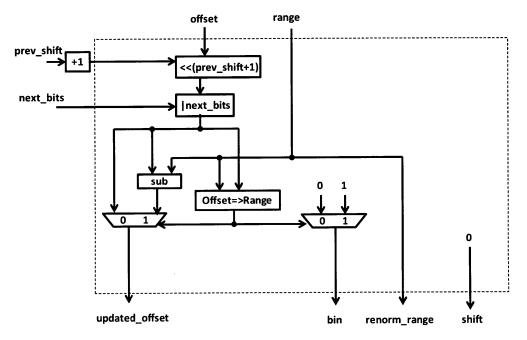

| 4-8  | Bypass decoding path                                                                                                                  | 117 |

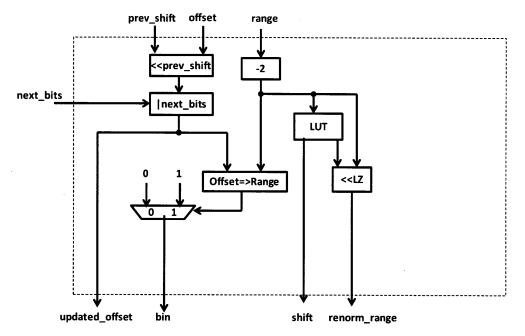

| 4-9  | Terminate decoding path                                                                                                               | 118 |

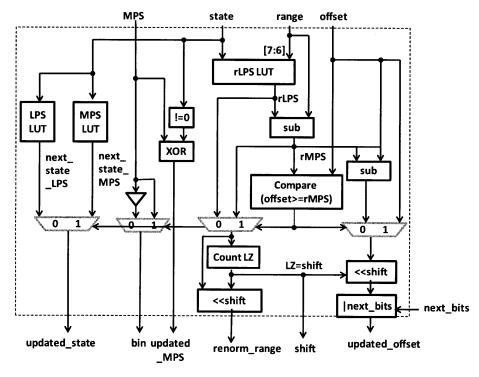

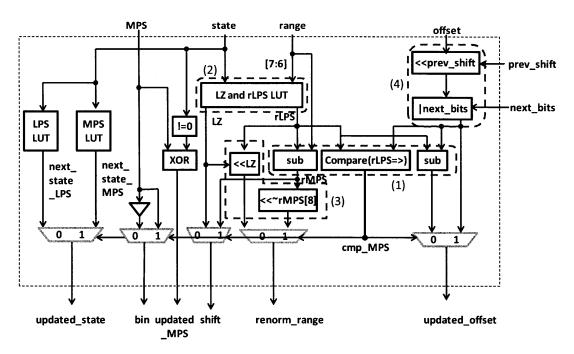

| 4-10 | Binary arithmetic decoding architecture mapped directly from data flow in                                                             |     |

|      | Fig. 4-11                                                                                                                             | 118 |

|      | Data flow in binary arithmetic decoder                                                                                                | 119 |

| 4-12 | Binary arithmetic decoding architecture optimized for reduced critical path                                                           |     |

|      | delay. Highlighted optimizations include (1) Range Comparison Reordering                                                              |     |

|      | (2) Leading Zero LUT (3) Early Range Shifting (4) Next Cycle Offset Renor-                                                            |     |

|      | malization                                                                                                                            | 120 |

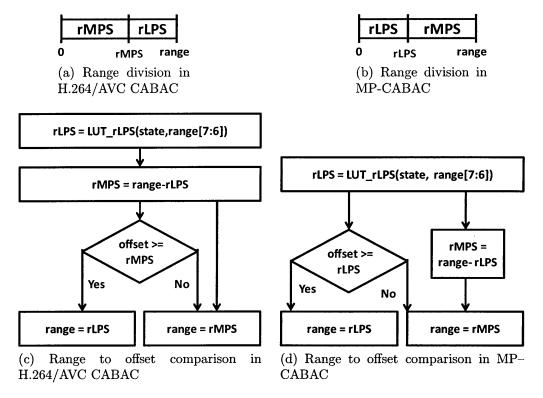

|      | Range comparison reordering for critical path reduction                                                                               | 121 |

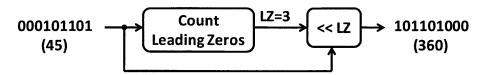

|      | Range renormalization flow                                                                                                            | 122 |

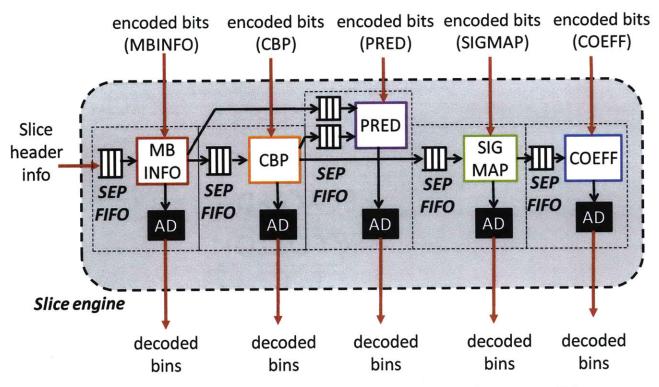

| 4-15 | The slices engines architecture used to decode SEP in parallel                                                                        | 123 |

| 4-10 | Context selection unite state machine (FSM)                                        | 124  |

|------|------------------------------------------------------------------------------------|------|

| 4-17 | FSM for SEP. The states of the FSM in Fig. 4-17 are color-coded to map to          |      |

|      | the different partition engines in Fig. 4-15 (MBINFO - red, PRED - purple,         |      |

|      | CBP - orange, SIGMAP - green, COEFF - blue)                                        | 125  |

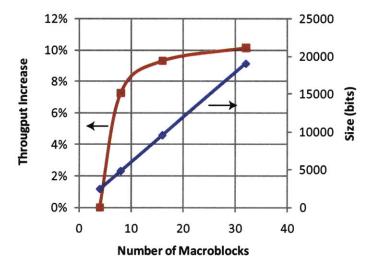

| 4-18 | Tradeoffs between depth of SEP FIFOs in macroblocks versus improvement             |      |

|      | in slice engine throughput and memory size. Throughput results are averaged        |      |

|      | across parkrun and bigships sequences with various quantization parameter          |      |

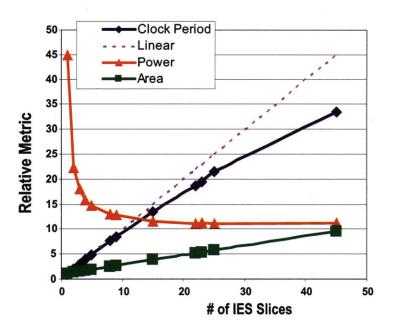

|      | (QP) and prediction structures                                                     | 127  |

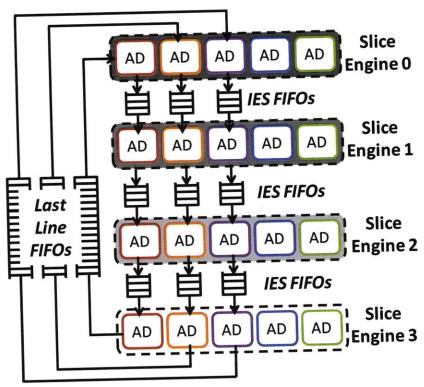

| 4-19 | The slices engines are connected using FIFOs to process IES in parallel            | 128  |

| 4-20 | Last line buffer is inserted between slice engine 0 and 3, so that slice engine 0  |      |

|      | can access the row above, which was decoded by slice engine 3, after wrapping      |      |

|      | to the next line                                                                   | 129  |

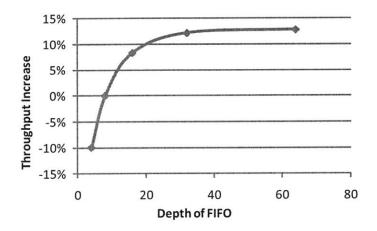

| 4-21 | Tradeoff between depth of IES FIFOs in macroblocks versus improvement in           |      |

|      | throughput based on simulation of bigships QP=27, IBBP, IES=8                      | 129  |

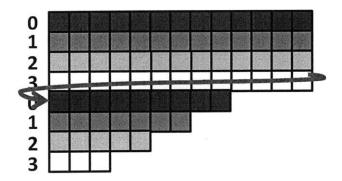

| 4-22 | Rotate slice engine that process first row in frame to prevent idle slice engines  |      |

|      | when the number of rows in frame is not a multiple of the number of IES            | 132  |

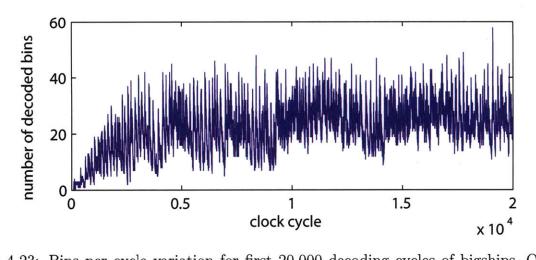

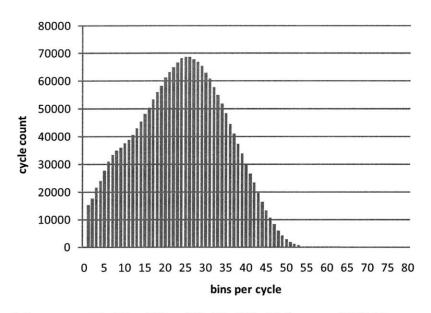

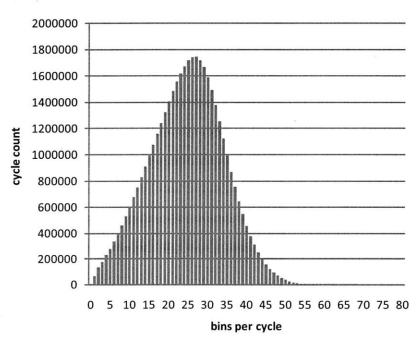

| 4-23 | Bins per cycle variation for first 20,000 decoding cycles of bigships, QP=27,      |      |

|      | IES=16                                                                             | 133  |

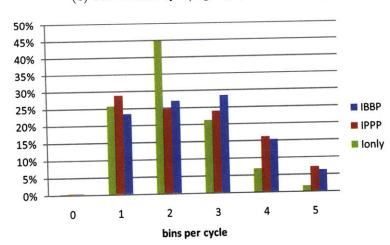

| 4-24 | Bins per cycle distributions for different sequences, QP and prediction structures | .134 |

|      | Bins per cycle distributions for 16 IES per frame.                                 | 136  |

|      | Post layout area breakdown of MP-CABAC                                             | 138  |

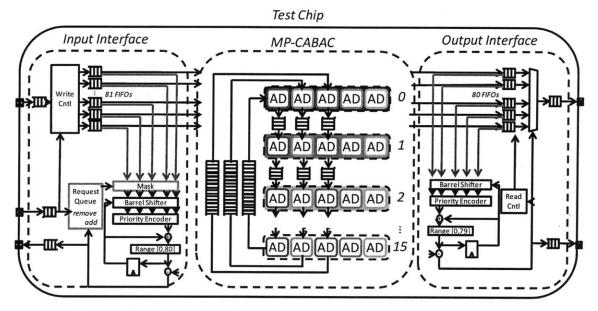

| 5-1  | Top level architecture of MP-CABAC test chip. MP-CABAC is implemented              |      |

|      | with 16 slice engines                                                              | 142  |

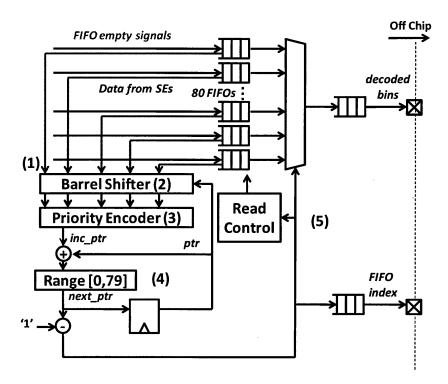

| 5-2  | Round robin control for output of MP-CABAC                                         | 144  |

| 5-3  | Round robin control for input of MP-CABAC                                          | 145  |

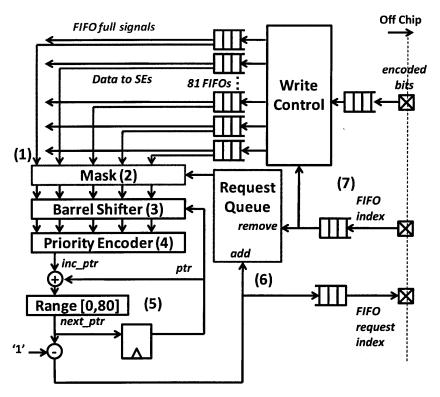

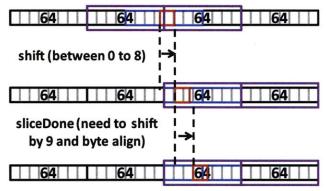

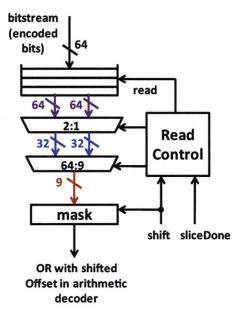

| 5-4  | Bitstream control used to map new bits from input FIFOs to arithmetic decoder      | 147  |

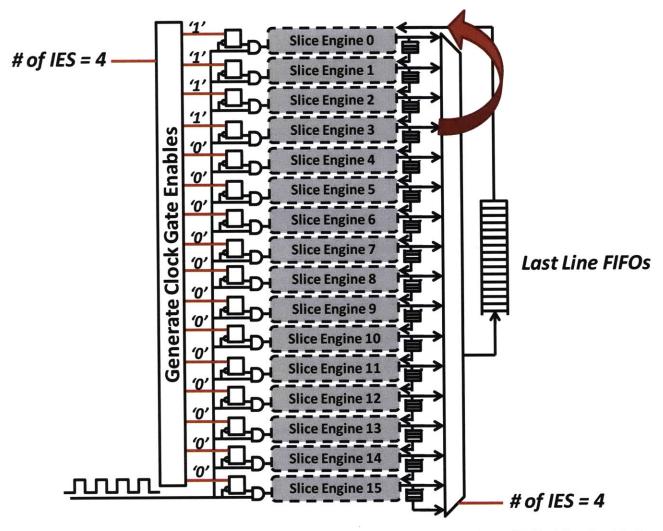

| 5-5  | The architecture is configurable to support different number of IES. The           |      |

|      | disabled slice engines are clock gated. In the above example, the architecture     |      |

|      | can support up to 16 IES and is configured to process four                         | 148  |

| 5-6  | Global signals routed to all slice engines                                         | 148  |

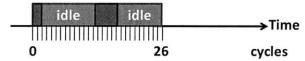

| 5-7  | A illustration of how bins per cycle and bin-rate changes when core frequency      |      |

|      | is increased. The idle time remains the same regardless of core frequency since    |      |

|      | it is dictated by the interface bottleneck. However, active time is reduced        |      |

|      | by 4x since the time per cycle is reduced. Thus, at higher frequency the           |      |

|      | proportion of idle cycles to total cycles increases, which reduced the bins per    |      |

|      | cycle. However, the time to decode all bins decreases, so the overall bin-rate     |      |

|      | increases                                                                          | 149  |

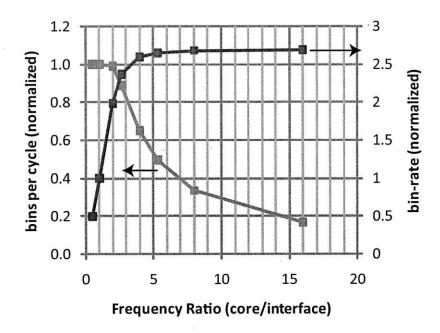

| 5-8  | Impact of increasing the core frequency above the interface frequency on bin-      |      |

|      | rate and bins per cycle. (Simulated on bigships, IES=16, IBBP, QP=27) $$ .         | 150  |

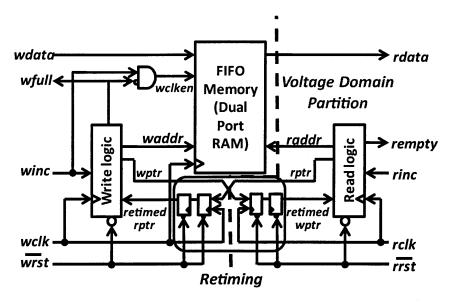

| 5-9  | Asynchronous FIFO used between interface and core domain. This figure is           |      |

|      | adopted from [88]                                                                  | 151  |

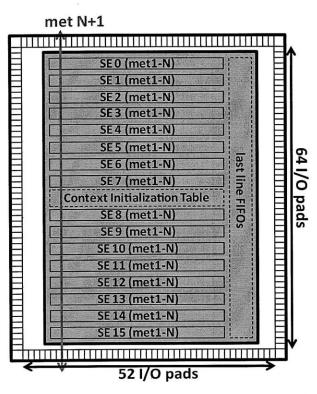

| 5-10       | restricted to layers 1-N, such that layer N could be dedicated to connecting the slice engines. Shaded area represents the core domain. White area represents the interface domain.                                                                                                                                                                                                              | 152 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

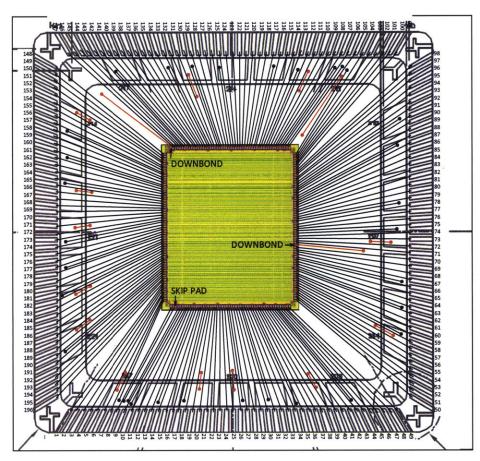

| 5-11       |                                                                                                                                                                                                                                                                                                                                                                                                  | 153 |

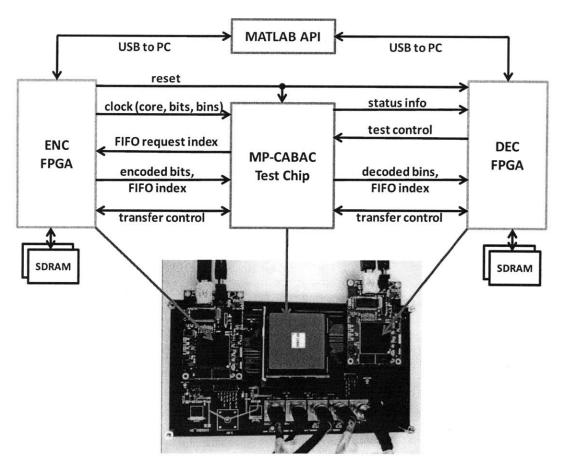

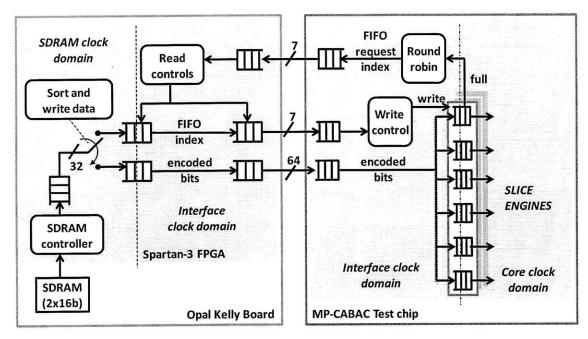

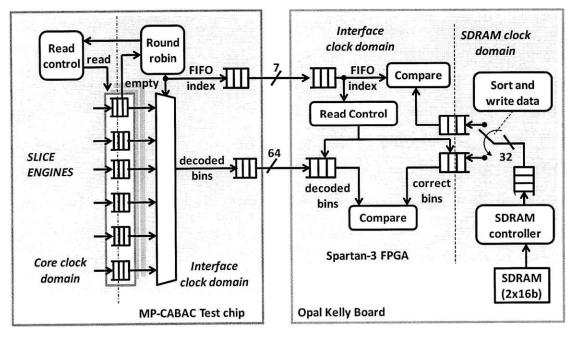

|            | 1                                                                                                                                                                                                                                                                                                                                                                                                | 154 |

|            |                                                                                                                                                                                                                                                                                                                                                                                                  | 154 |

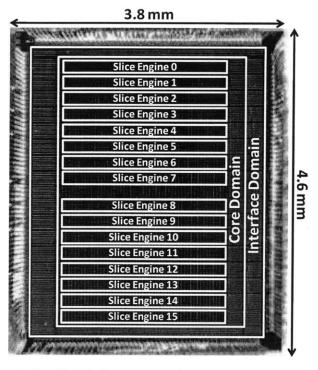

|            | Die photo of MP-CABAC test chip (domains and slice engines are highlighted).                                                                                                                                                                                                                                                                                                                     | 156 |

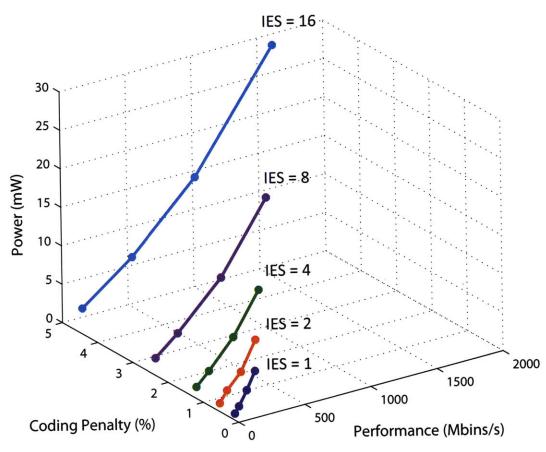

|            | Tradeoff between power-performance-coding penalty for bigships, QP=27, IBBP. Each line represents a fixed number of IES and consequently a fixed                                                                                                                                                                                                                                                 | 158 |

| 5_16       | Power-performance tradeoff for various numbers of IES in bigships, QP=27,                                                                                                                                                                                                                                                                                                                        | 100 |

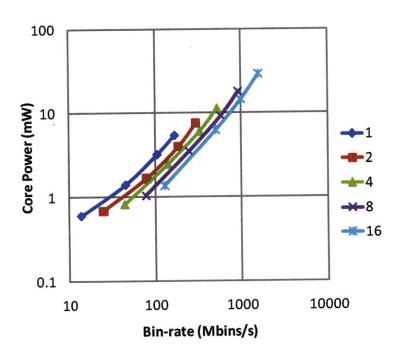

| 0-10       |                                                                                                                                                                                                                                                                                                                                                                                                  | 159 |

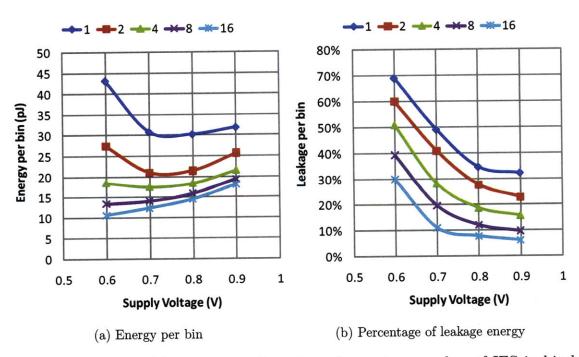

| 5-17       | Energy per bin versus supply voltage for various number of IES in bigships, QP=27, IBBP                                                                                                                                                                                                                                                                                                          | 159 |

| 5_18       | <b>~</b> ,                                                                                                                                                                                                                                                                                                                                                                                       | 161 |

|            | ν=                                                                                                                                                                                                                                                                                                                                                                                               | 162 |

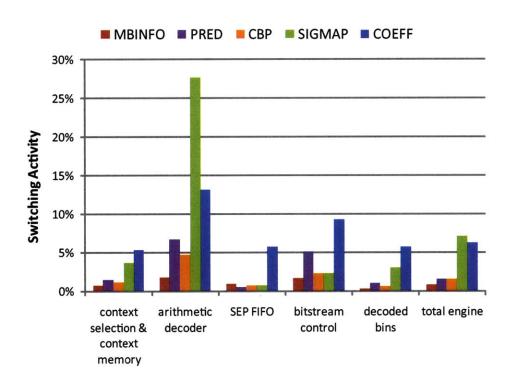

|            | The switching activity of different components in a slice engine of MP-CABAC,                                                                                                                                                                                                                                                                                                                    | 163 |

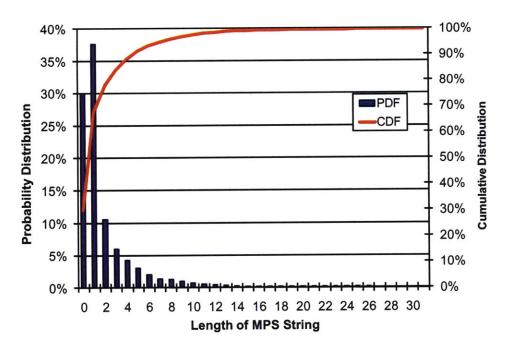

|            | sequences). As the length of the MPS string increases, it is less likely to occur.                                                                                                                                                                                                                                                                                                               | 175 |

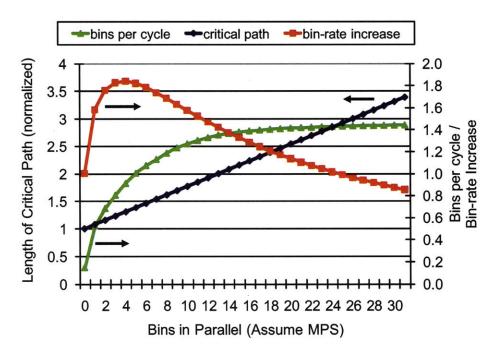

| A-2        | Impact of number of bins on throughput, critical path and bin-rate. Plot assumes that each additional bin increases the critical path by 7.7%                                                                                                                                                                                                                                                    | 176 |