Jigsaw puzzle analogy

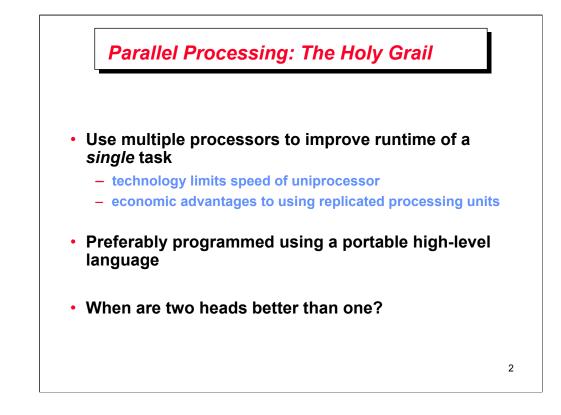

Number crunching apps

Claim that weather forecasts are accurate over 5 days, and would like to improve that.

Nonlinear phenomena.

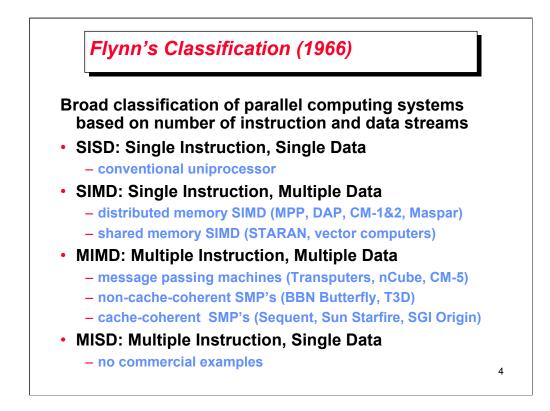

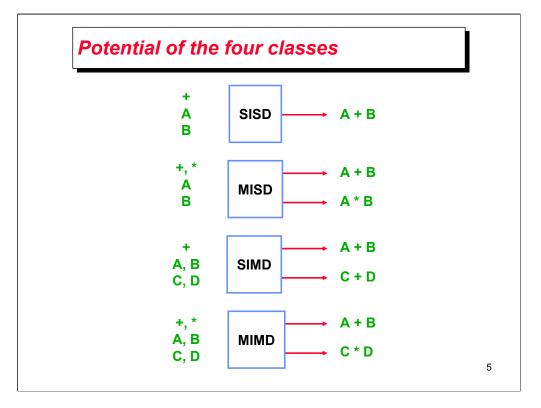

MISD, check that a number is prime, do a divide on the same number with Processor number I.

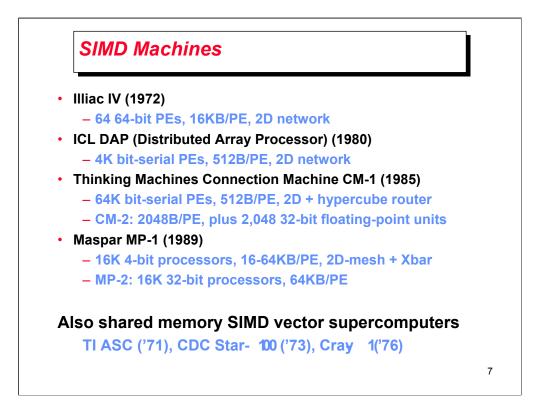

Illiac IV: \$31M instead of \$8M paid by DARPA, Illiaction Glypnir language: Norse mythological rope that controls a vicious animal

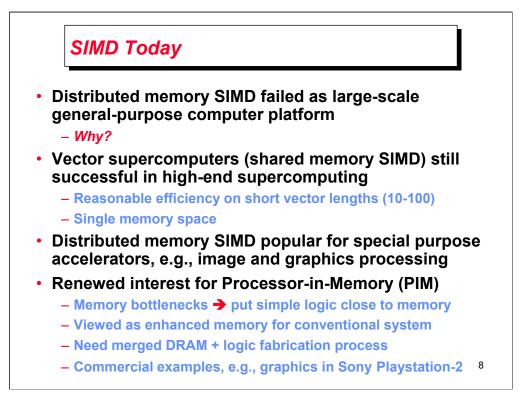

Required huge quantities of data parallelism (> 10000 elements) Required programmer-controlled distributed data layout.

Thinking machines, interconnect network a FAT-TREE.

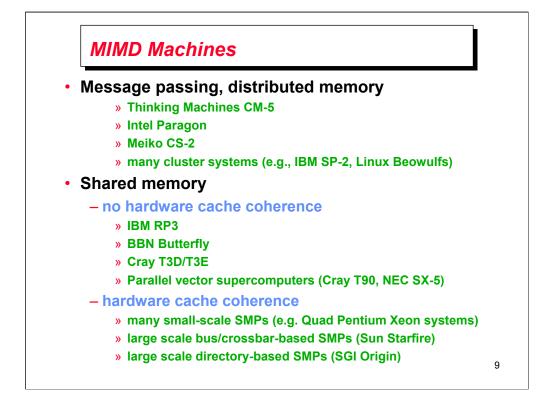

Rp3: research parallel processor prototype

BBN": Bolt Beranek and Newman, A spiffy interconnect will not by itself

Allow the construction of a supercomputer out of common household appliances.

Problem was the commodity processors did not support multiple outstanding

Memory requests. So the remote memory access killed off performance, unless

Excellent data layout was achieved. So it lost to message-passing networks.

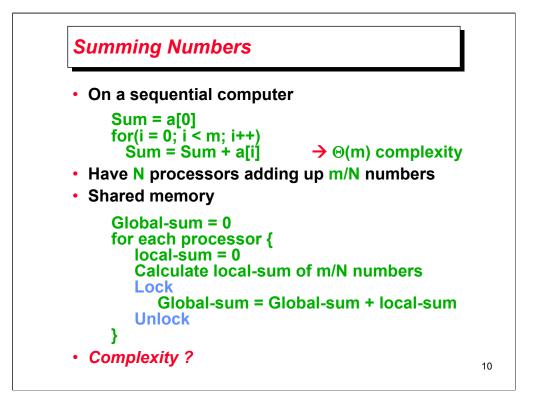

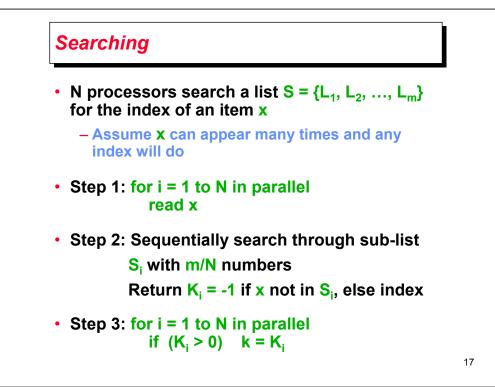

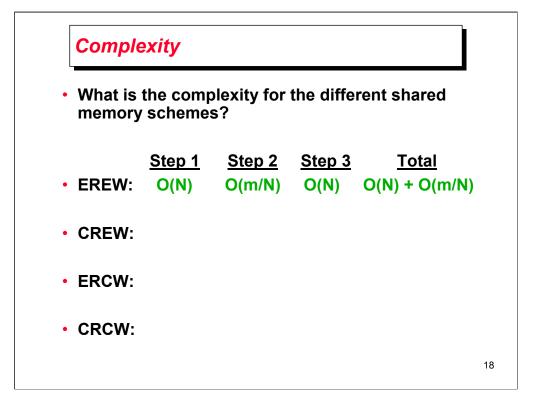

## Theta(m/N) + Theta(N)

Theta(N) comes from summing N numbers in series.

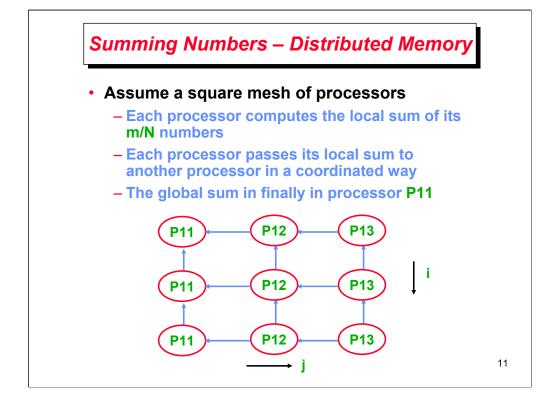

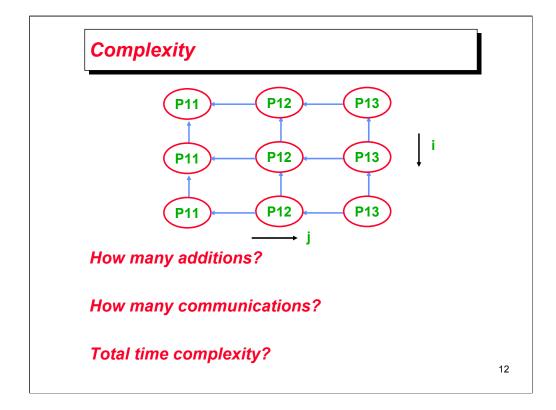

Sqrt(N) – 1 additions, sqrt(N) - 1 communications in each direction Theta(m/N) + Theta(sqrt(N)) + C, C is cost of communication

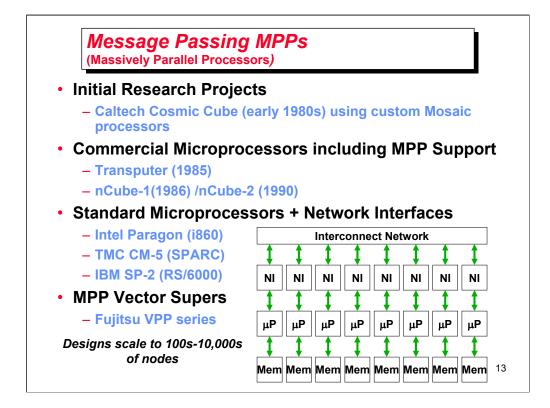

Read up on Cosmic Cube, transputer, CM5 other machines.

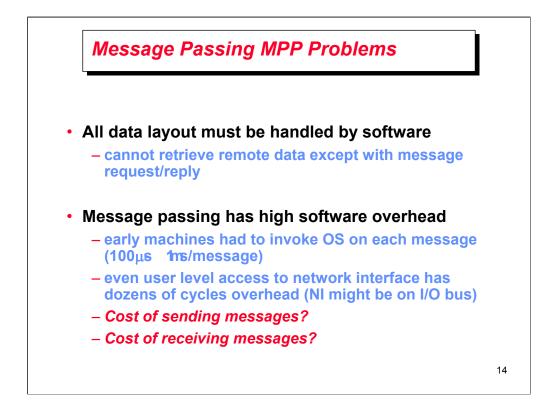

Sending can be cheap (like stores)

Receiving is expensive, need to poll or interrupt.

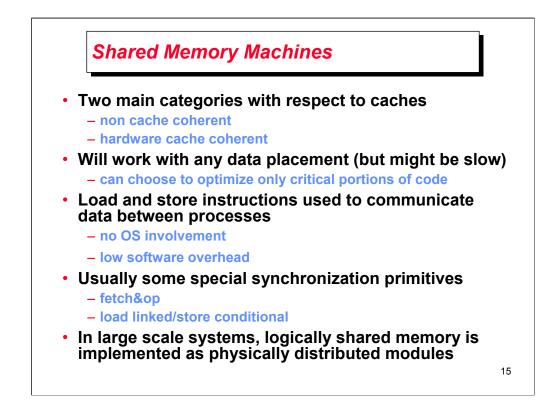

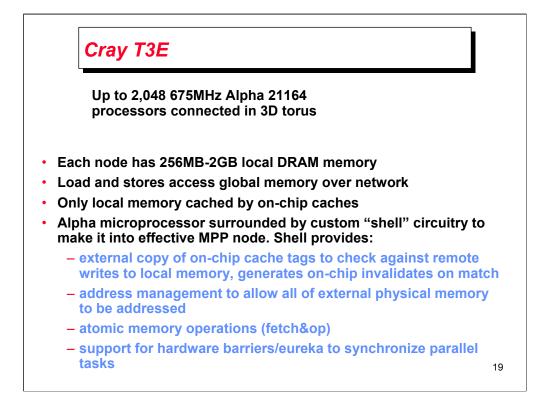

Read up on no hardware coherence for the Cray T3E, eureka?

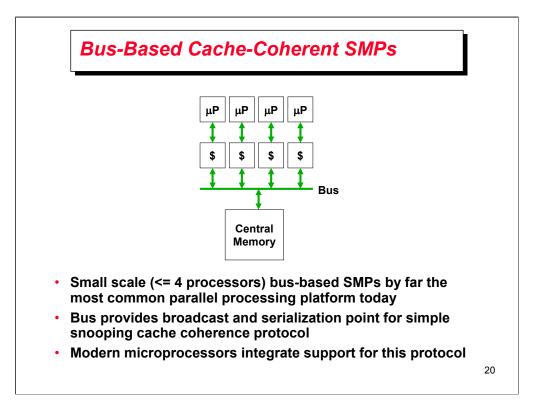

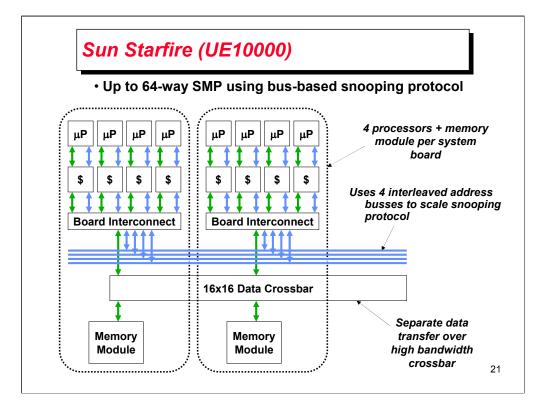

Interleaved multiple address busses. Hardest part of scaling up an SMP system is its coherence bandwidth.

Read Starmicro paper.

Read up on directories, and compare to snoopy protocols.

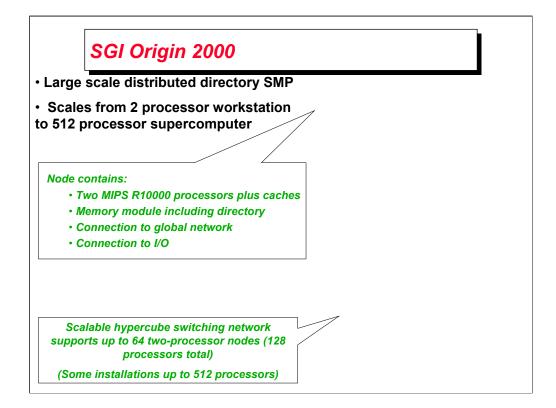

SGI origin paper.

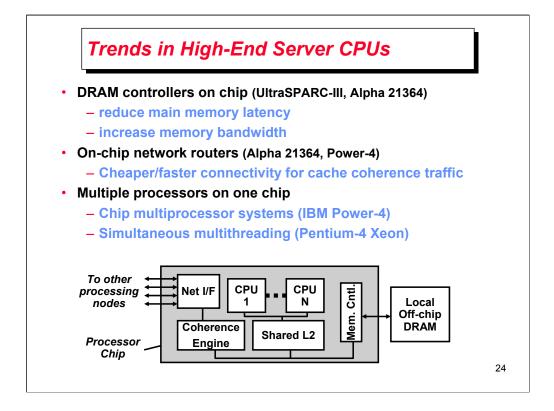

INTEGRATION in VLSI. DRAM controllers on chip to reduce main memory latency (250ns to 170 ns in Ultrasparc III) and

Increase memory bandwidth - 12 GB/s over 8 Rambus channels in 21364.

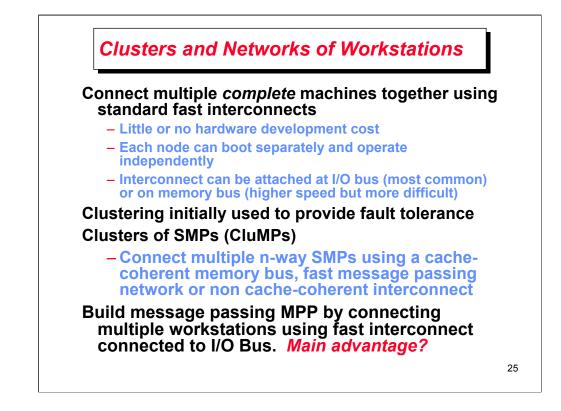

HP Exemplar cache coherent, SGI Power Challenge Array, Vector supercomputers NEC SX-5

Ucberkeley NOW, 100 Sun workstations connected by a Myrinet network. What is Myrinet?

Sold commercially by IBM (SP-2), and Cray selling networks of Alpha's.

| The Future? |  |  |  |  |

|-------------|--|--|--|--|

|             |  |  |  |  |

|             |  |  |  |  |

|             |  |  |  |  |

|             |  |  |  |  |

|             |  |  |  |  |

|             |  |  |  |  |

|             |  |  |  |  |