# THE DESIGN AND CONSTRUCTION OF A SPECIAL PURPOSE COMPUTER FOR SPEECH SYNTHESIS-BY-RULE

by

Robert Jay Steingart

SB, Massachusetts Institute of Technology

(1974)

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May, 1976

| Signature | of | AuthorDepartment of Electrical Engineering |

|-----------|----|--------------------------------------------|

|           |    | and Computer Science, March 31, 1976       |

Certified by..... Thesis Supervisor

Accepted by ..... Donartmental Committee on

Chairman, Departmental Committee on Graduate Students

THE DESIGN AND CONSTRUCTION OF A SPECIAL PURPOSE COMPUTER FOR SPEECH SYNTHESIS-BY-RULE

by

Robert Jay Steingart

Submitted to the Department of Electrical Engineering and Computer Science on March 31, 1976 in partial full-fillment of the requirements for the Degree of Master of Science.

#### Abstract

The special purpose computer described in this thesis is designed to convert an input string of phonemes, together with prosodic information, into a set of vocal tract model parameters. A post-processor uses these parameters to produce natural sounding synthetic speech. Three major requirements necessitated the development of a processor with a customized architecture and instruction set: real-time processing capability, low cost, and compact size. Efficient, high-speed operation has been ensured by matching the processor hardware and software with the algorithmic needs of the specific task. The processor has been designed, constructed, and tested.

THESIS SUPERVISOR: Jonathan Allen

TITLE: Professor of Electrical Engineering

#### **ACKNOWLEDGEMENT**

I would like to thank my thesis advisor, Prof.

Jonathan Allen for suggesting the topic of research.

He helped oversee and direct the plan of research, and was instrumental in obtaining the requisite funds.

Discussions in the early stages of design with former staff member Eric Jensen proved to be extremely informative. He was most helpful for his advice concerning the instruction set design.

Jack Allweiss modified and helped in the use of the wirewrap programs to convert the logic diagrams into hardwired boards.

The final draft was edited and typed with the kind assistance of Mark Johnston.

I would also like to thank other members of the group for their ideas and comments at various times over the course of this research.

## TABLE OF CONTENTS

|          |      |                                                                     | Page                                   |

|----------|------|---------------------------------------------------------------------|----------------------------------------|

| Title Pa | age. | • • • • • • • • • • • • • • • • • • • •                             | 1                                      |

| Abstract | t    |                                                                     | 2                                      |

| Acknowle | edge | ement                                                               | 3                                      |

| List of  | Fi   | gures                                                               | 6                                      |

| Chapter  | 1    | Introduction                                                        | 8<br>8<br>9<br>12                      |

| Chapter  | 2    | Speech Synthesis by Rule-The Klatt Model. 2.1 The Vocal Tract Model | 16<br>17<br>22<br>24                   |

| Chapter  | 3    | Instruction Set Design                                              | 33<br>37<br>40<br>53<br>58<br>59       |

| Chapter  | 4    | Computer Architecture                                               | 62<br>64<br>65<br>67<br>70<br>73<br>85 |

| Chapter  | 5    | Algorithms and Microcode                                            | 93<br>93<br>98<br>104                  |

| Chapter  | 6    | Hardware Implementation                                             | 112<br>112<br>114                      |

# TABLE OF CONTENTS (cont.)

|                                        |                                                                             | Page                                          |

|----------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------|

| 6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8 | Timing Component Layout and Chip Count Front Panel Wirewrapping Performance | 116<br>118<br>121<br>133<br>136<br>138<br>139 |

| Appendix A H                           | lardware Schematics                                                         | 141                                           |

| Appendix B M                           | icroword and Data Flow Graphs                                               | 149                                           |

| Appendix C M                           | Macroinstruction Mnemonics and Formats.                                     | 163                                           |

| Bibliography a                         | and References                                                              | 165                                           |

# List of Figures

| Figure |                                              | Page |

|--------|----------------------------------------------|------|

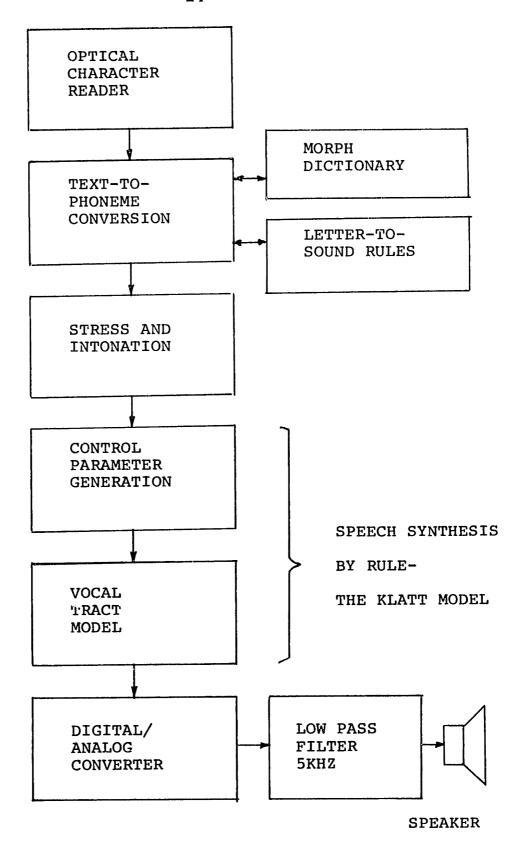

| 1      | Block Diagram of the Text-to-Speech System   | 14   |

| 2      | Difference Equation to Realize Digital       |      |

|        | Resonator                                    | 18   |

| 3      | Vocal Tract Model                            | 20   |

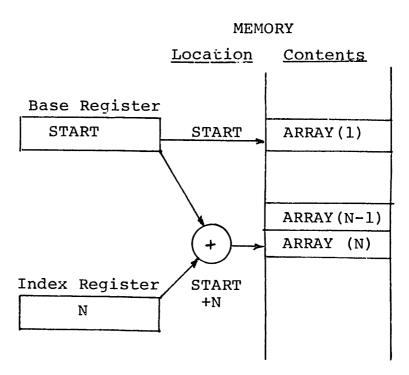

| 4      | Indexed Addressing of Arrays                 | 25   |

| 5      | Section of Flowchart Exhibiting Feature      |      |

|        | Testing                                      | 26   |

| 6      | General Architecture for Speech Synthesis    |      |

|        | Computed                                     | 63   |

| 7      | CPU Architecture                             | 71   |

| 8      | 44 Bit Microword Format                      | 76   |

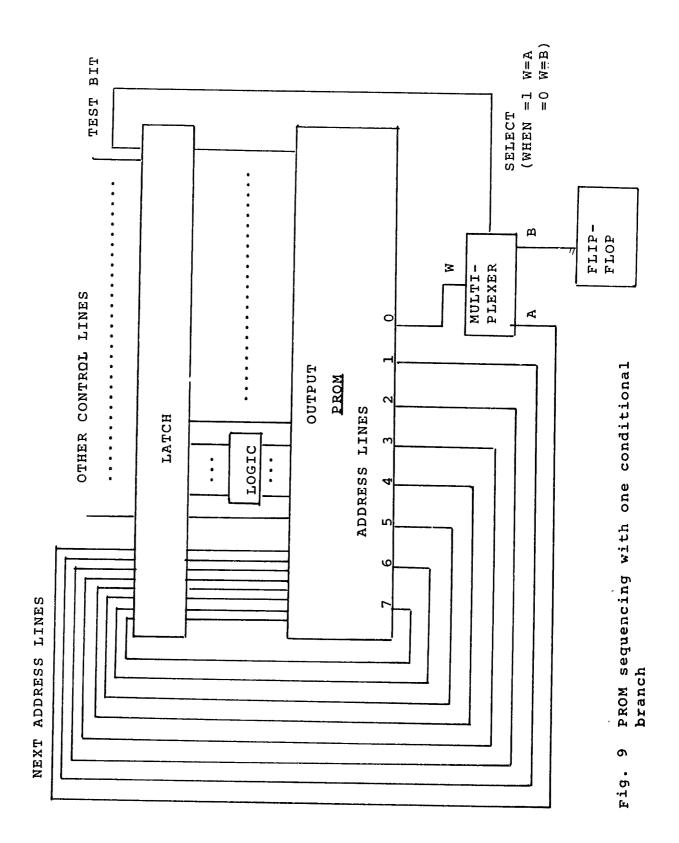

| 9      | PROM Sequencing with One Conditional Branch  | 79   |

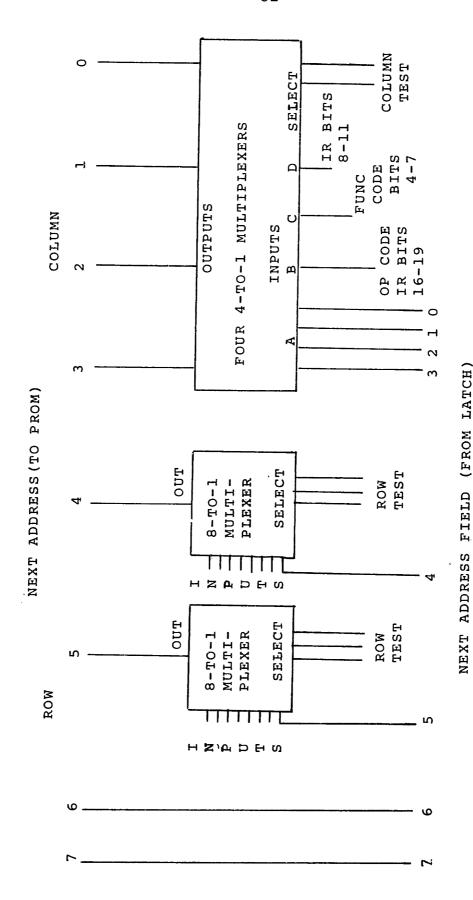

| 10     | Actual PROM Sequencer                        | 82   |

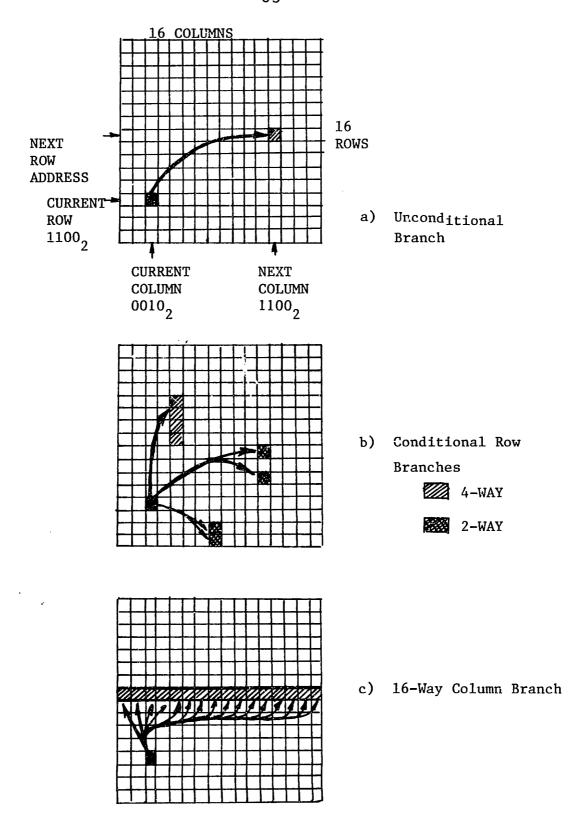

| 11     | Microcode Branches                           | 83   |

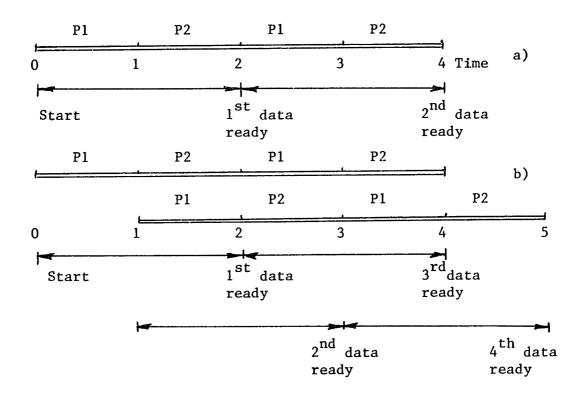

| 12     | Simple Example of Pipelining                 | 86   |

| 13     | Overlap Fetching of Microinstructions        | 87   |

| 14     | Effects of Parallel Processing on            |      |

|        | Macroinstruction Execution Speed             | 89   |

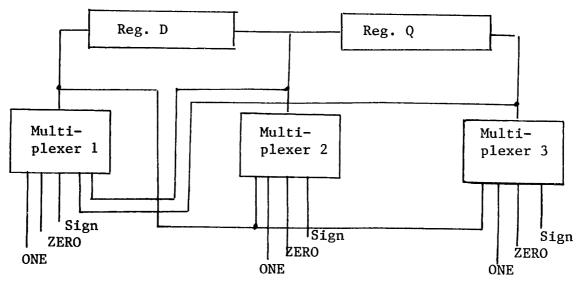

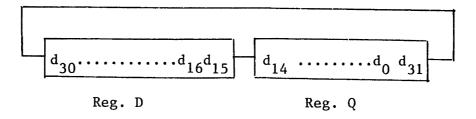

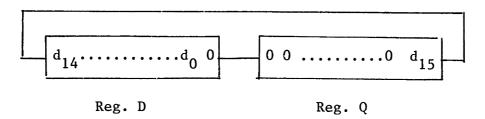

| 15     | SHIFT Logic                                  | 94   |

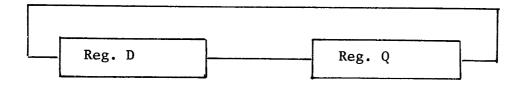

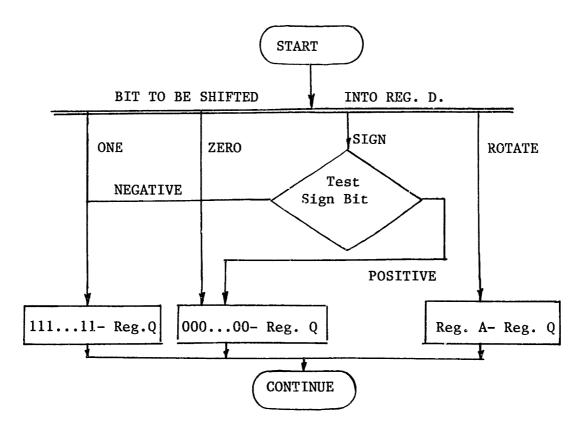

| 16     | Initialization of Register Q for Shift       | 95   |

| 17     | Flowchart for Restoring Division of Positive |      |

|        | Numbers                                      | 105  |

# List of Figures (cont.)

| Figure |                                        | Page |

|--------|----------------------------------------|------|

| 18     | Flowchart for Nonrestoring Division of |      |

|        | Positive Numbers                       | 108  |

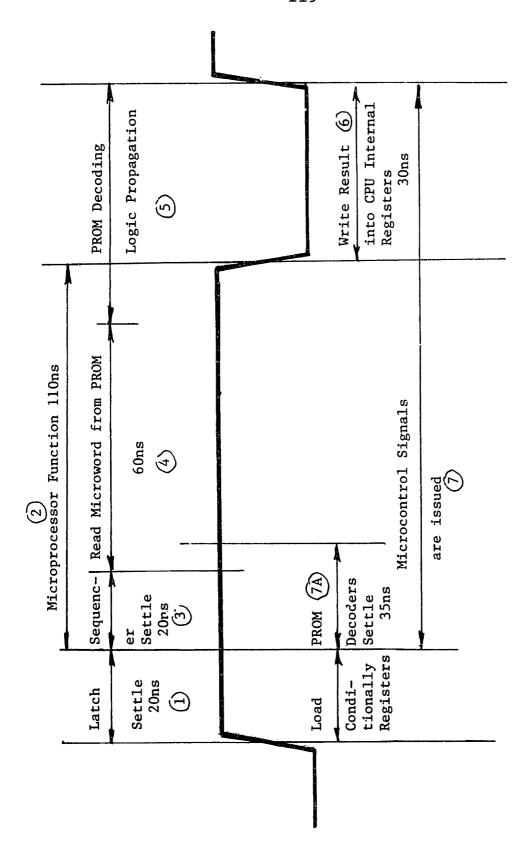

| 19     | Worst Case System Timing               | 119  |

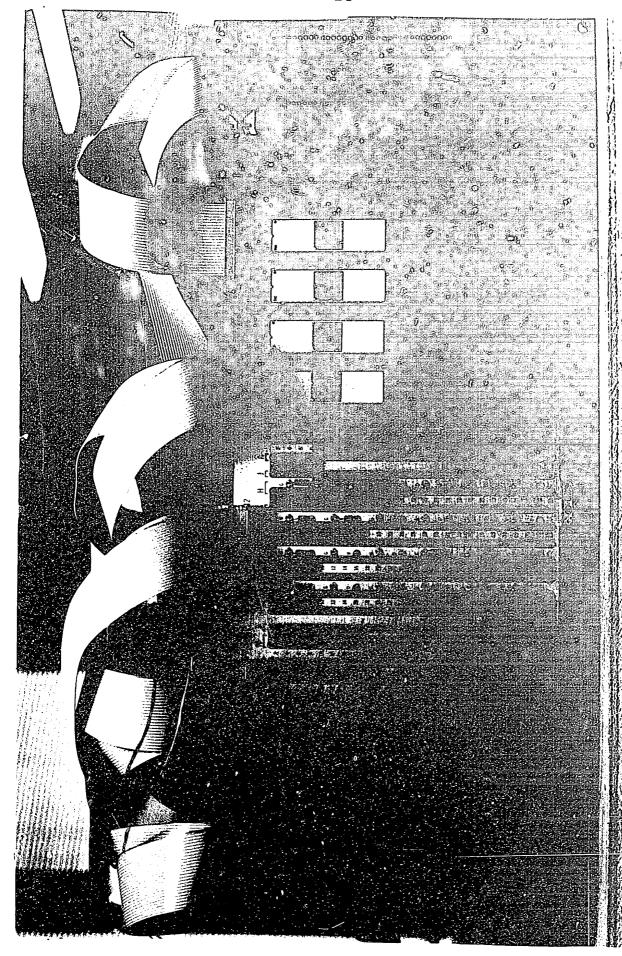

| 20     | Speech Processor-Rear View             | 122  |

| 21     | CPU Board                              | 123  |

| 22     | Memory Board                           | 124  |

| 23     | Front Panel                            | 125  |

| 24     | Underside of Wirewrapped Board         | 126  |

| 25     | Boards Hinged for Testing              | 126  |

| 26     | Back View of Front Panel               | 126  |

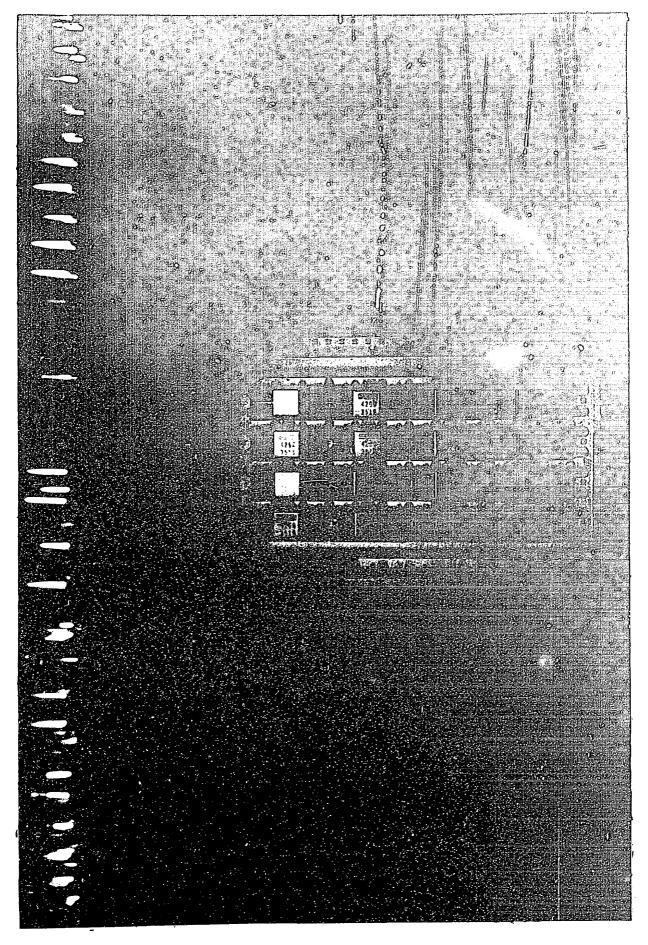

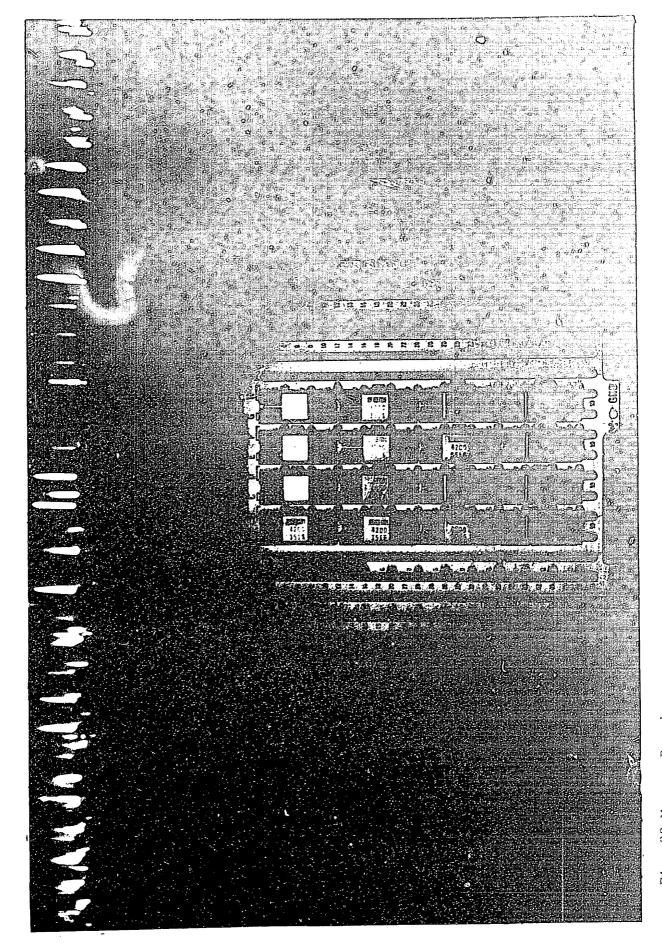

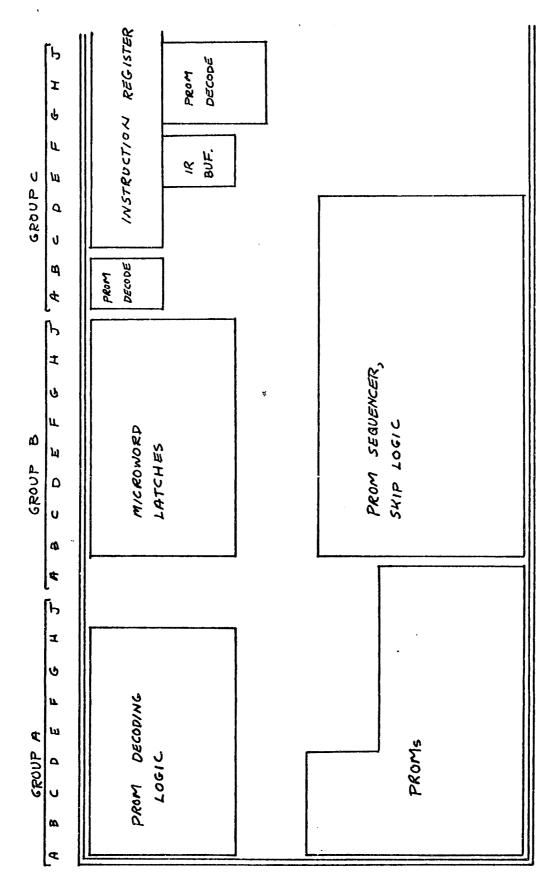

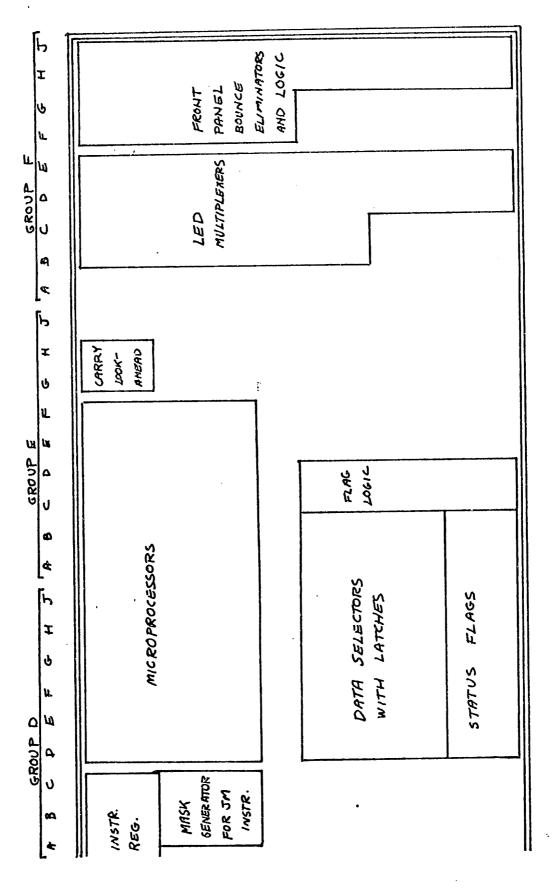

| 27     | Chip Layout for CPU Board              | 127  |

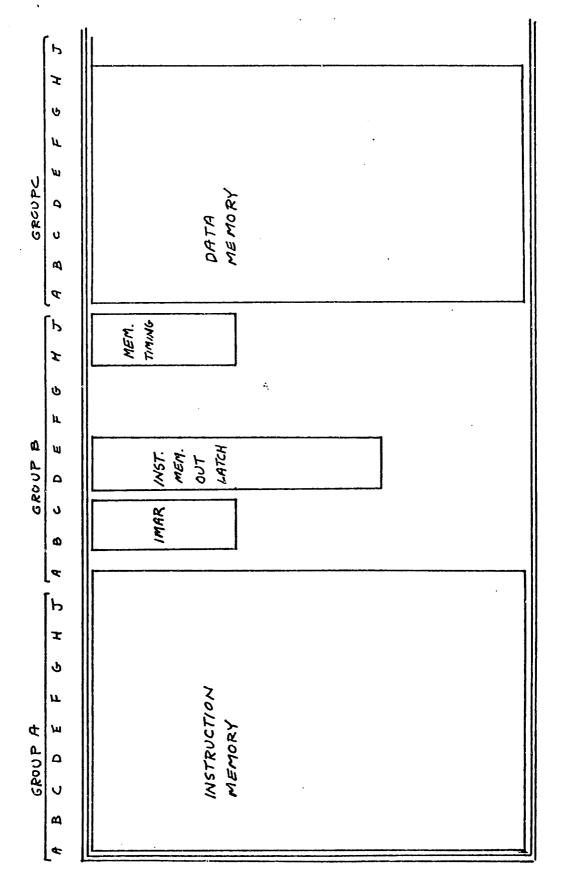

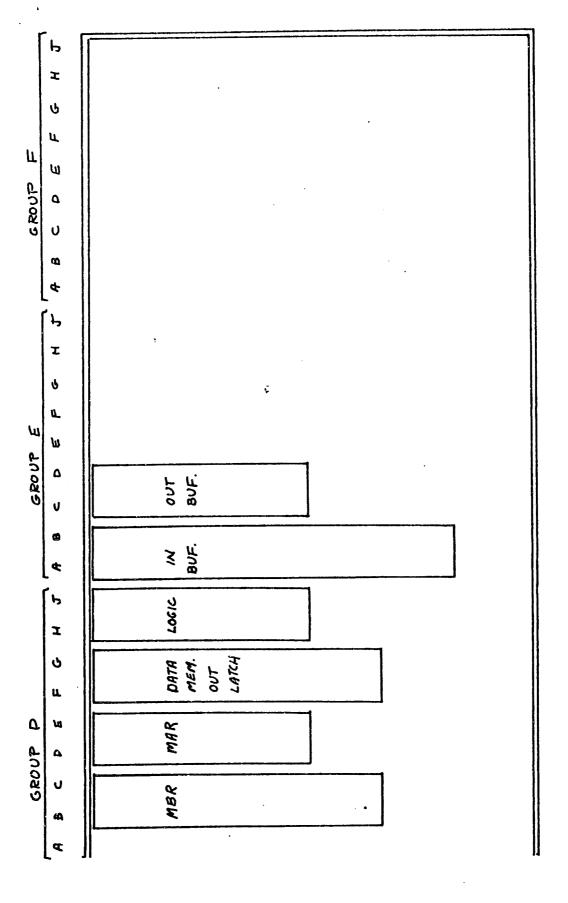

| 28     | Chip Layout for Memory Board           | 129  |

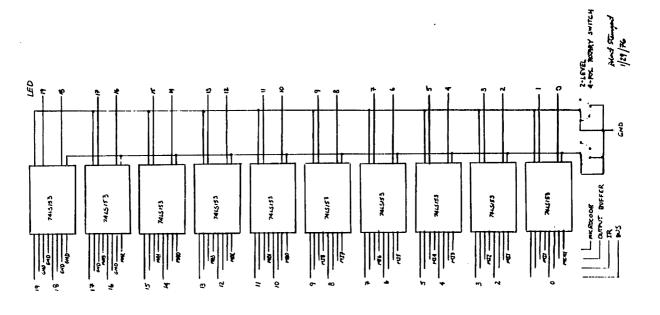

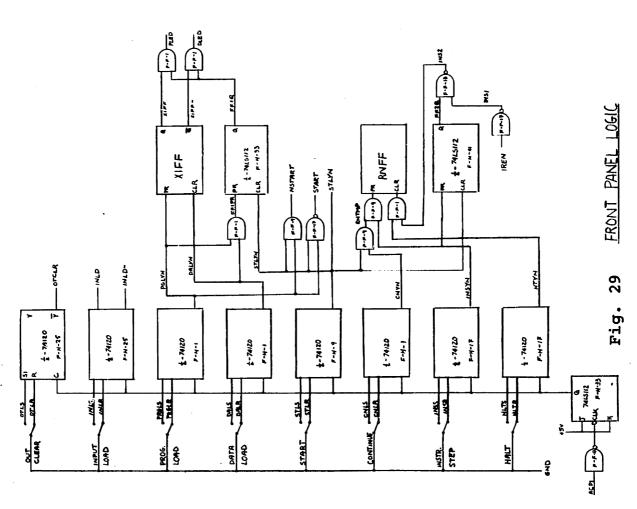

| 29     | Front Panel Logic                      | 142  |

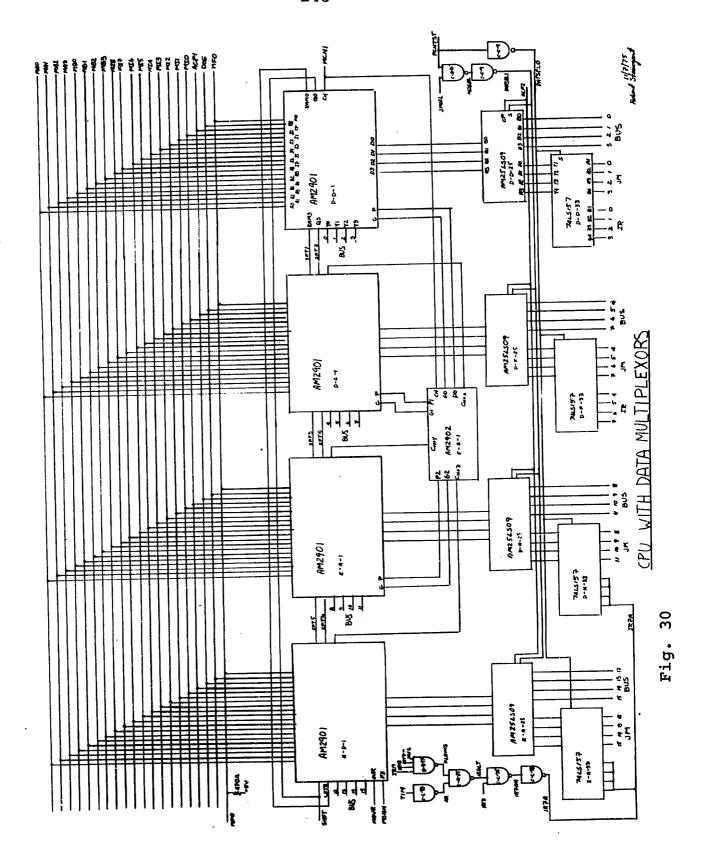

| 30     | CPU with Data Multiplexers             | 143  |

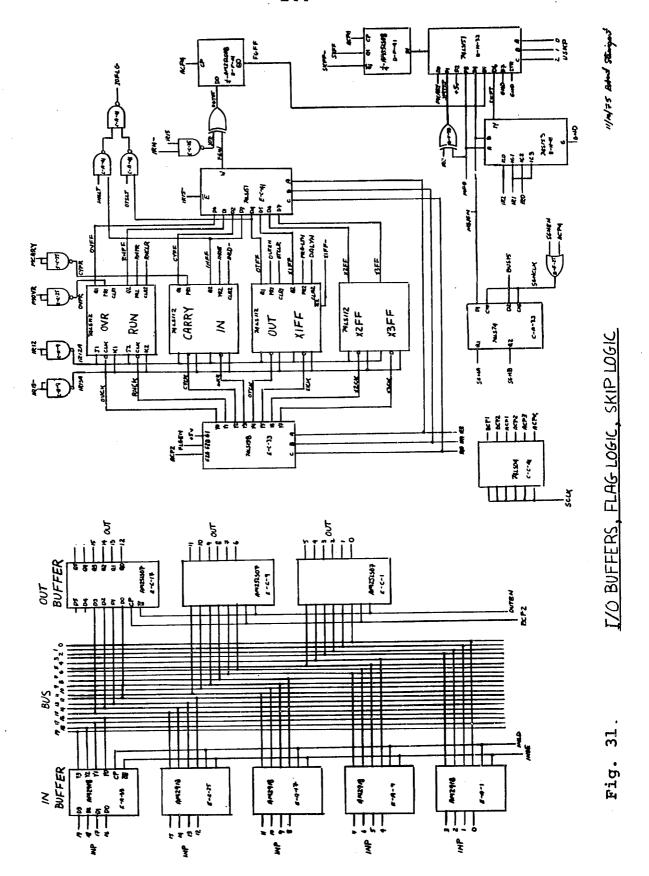

| 31     | I/O Buffers, Flag Logic, Skip Logic    | 144  |

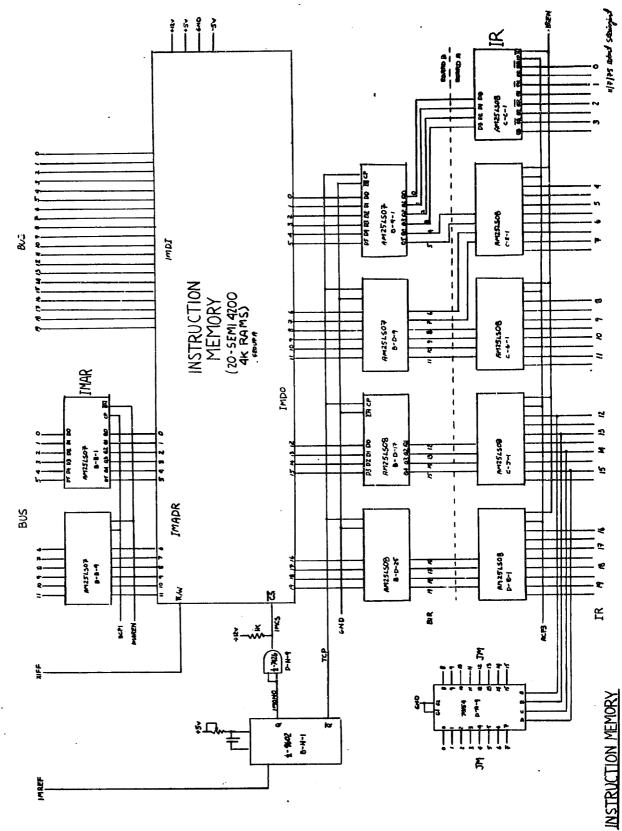

| 32     | Instruction Mmeory                     | 145  |

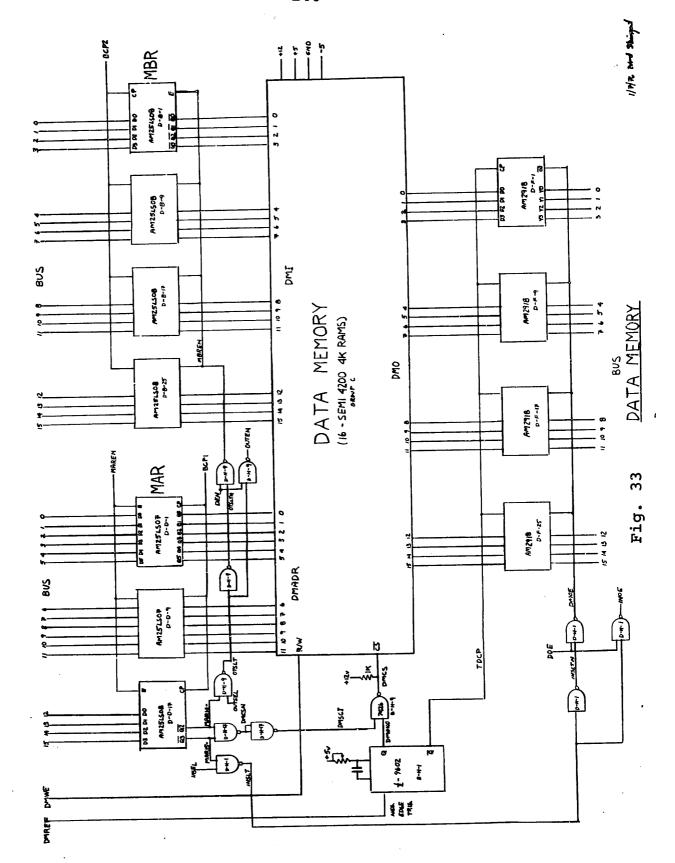

| 33     | Data Memory                            | 146  |

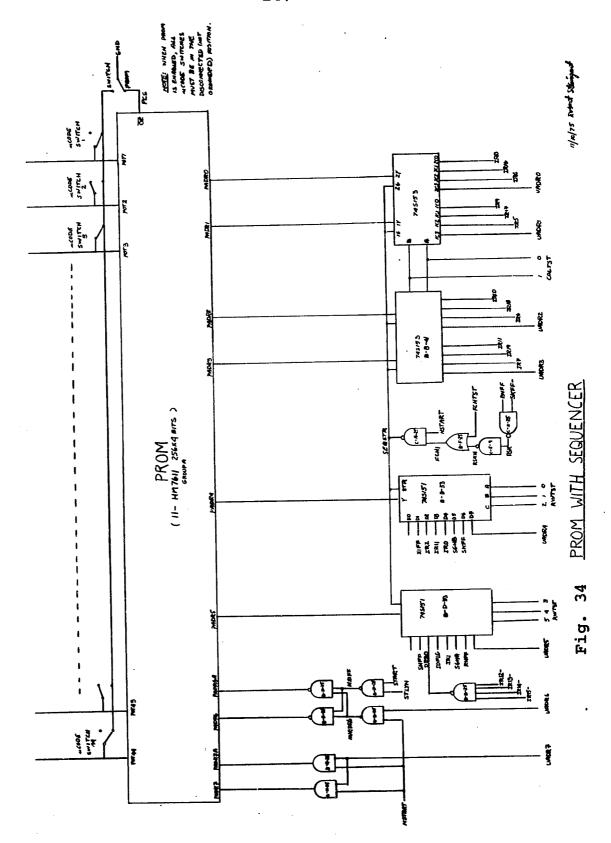

| 34     | PROM with Sequencer                    | 147  |

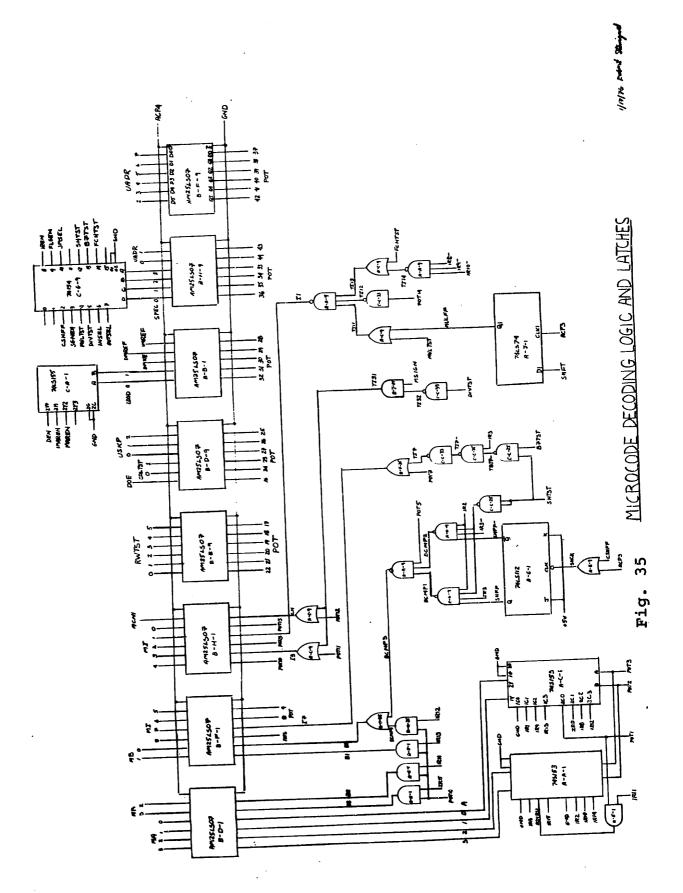

| 35     | Microcode Decoding Logic and Latches   | 148  |

#### CHAPTER 1

### 1.1 Introduction

The development of machines capable of producing synthetic speech has been an area of active research for decades. Early devices, dating back to the nineteenth century, employed mechanical bellows, reeds, switches, and acoustic resonant chambers, controlled by a person to mimic human speech. With practice, a trained operator could manually vary the system parameters to produce a few spoken words.

Recent advances in linguistic theory, digital computers, and digital signal processing have led to electronic analogs of the vocal tract with parameters that can be updated easily and accurately under computer control. Such systems require a large number of computations, and real-time speech production requires large and expensive computers. Rapid technological development in large-scale integrated (LSI) circuitry, however, is having a tremendous impact on the size, price, and speed of digital computing machines. These advances are instrumental in changing speech synthesis from merely a laboratory curiosity into a practical device for institutional or even individual use.

The subject of this thesis is the design and construc-

tion of a processor, using state-of-the-art technology, to implement a compact, inexpensive, natural sounding speech synthesizer capable of real-time speech production. These constraints necessitated the development of a special purpose digital computer, tailored for efficient execution of speech synthesis programs. The machine has been successfully built and tested. The prototype includes approximately 150 integrated circuits and costs under \$3000. Current trends in LSI technology, coupled with large volume production, will certainly reduce the size and cost substantially. There is little doubt that the development of a practical, cost-effective speech synthesizer lies in the forseeable future.

## 1.2 Applications

The applications of speech synthesis hardware are plentiful. Throughout the years we have witnessed man's greater reliance on both mechanical and electrical machines. He has been forced, however, to communicate with machines on their level by using switches and keyboards for input, and printers and cathode ray tube displays for output. Since speech is perhaps man's most convenient form of communication, there is little question that the ability to speak to a machine and to receive a spoken response would greatly facilitate man-

to-machine communication.

Speech synthesis could provide for automatic voice readout of computer-stored information in a form easily assimilated by the human user. A user could request information from a central computer, perhaps over a telephone line, and the computer would respond verbally. Data could be entered either manually with a push button telephone as a keyboard or perhaps verbally once the accuracy of speech recognition devices is improved. Functions performed efficiently on large digital computers, such as automatic information retrieval and numerical computation, would be as far away as the nearest telephone. At present it seems most efficient to have both the phonemes and speech waveforms generated by the central computer, so that no special devices are employed at the terminals. However, once speech synthesizers are cheap enough, the waveform synthesis could be built into the terminals, thus greatly reducing the data channel bandwidth.

Channel bandwidth reduction may be another application of speech synthesis on crowded voice transmission lines. Reasonably accurate reproduction of speech from unencoded digitized samples requires approximately 50,000 bits/second. Delta modulation and pulse code modulation can reduce this figure by perhaps a factor of five, but

a system in which only phonemes and prosodic information is sent and reconstructed into speech by a synthesizer could conceivably operate at less than 100 bits/second. The bandwidth of existing speech channels could be increased by a factor of 500.

Although the savings in bandwidth is impressive, the conservation of channel capacity is not the overriding issue it once was (due to new broadband transmission techniques using lasers, fiber optics, and guided millimeter waves). Furthermore, to conserve bits in a speech synthesis transmission system, certain qualities of an individual's voice are lost, so all voices are more or less indistinguishable. So for the time being, speech synthesis will be attractive only for long-haul channels where bandwidth is still at a premium.

One of the most exciting applications of speech synthesis, and of particular interest to Professor Allen's group at MIT, is the development of reading machines for the blind. Ordinary books could be read with an optical scanner and the characters grouped together as phonemes. Phonemic and prosodic information would then be fed into the synthesizer which would produce speech. Such a machine would overcome the shortcomings of braille, which include the limited availability of braille documents and the difficulty in acquiring proficiency in braille, especially for the aged

and those with a loss of tactile sensitivity.

Deaf people and others with vocal impairment could also benefit from speech synthesis. A typewriter operated voice for those who cannot speak is certainly feasible.

In the more distant future, a translator from one foreign language to another could be built by coupling a speaking typewriter to an automatic voice recognition system.

Finally, a speech synthesizer with controls that closely model the human vocal tract could be used as a research tool. By varying the model's parameters one can perform detailed and controlled experiments on various aspects of human speech production and recognition. This will have application to the further understanding of the psychology and physiology of speech formation and perception.

## 1.3 The MIT Text-to-Speech System

In the applications mentioned above, the feasibility is dependent upon the availability of a small and inexpensive speech synthesizer capable of producing intelligible speech from unrestricted text. One possible approach to the problem would involve recording all the words in the vocabulary, digitizing the signals, and storing the

bits in a computer memory. Words to be spoken would simply be looked up in the memory and the bits would be reconstructed by a digital-to-analog convertor to produce speech. This system may be feasible for small vocabularies, but the English language contains hundreds of thousands of words and would require an unwieldy memory. In addition, there would be no flexibility to accommodate variations in intonation and stress based upon context. Producing speech by piecing together one word pre-recorded segments thus sounds very unnatural.

Speech synthesis without recourse to any vestige of human speech seems to be the most attractive alternative, since it allows a large and sophisticated vocabulary in a form flexible enough to generate arbitrary messages while minimizing storage requirements. An overview of the complete text-to-speech system being developed by the Natural Language Processing Group at MIT is shown in Fig. 1. This illustrates how the processor developed in this thesis fits into the larger picture. first block an optical character reader converts printed text into an alphanumeric list of characters. Ultimately it must be able to read a complete range of type fonts from bound books. In the next section this list is scanned to generate phonemes. An attempt is first made to decompose each word into its morphs, the basic build-

Fig. 1 Block diagram of the text-to-speech system

ing blocks of English words. The phonemic transcription is then looked up in the morph dictionary. If the word cannot be decomposed into morph entries of the lexicon, another program containing letter-to-sound rules is invoked to produce phonemes. Speech reconstituted from these phonemes sounds monotone as it lacks stress and intonation information: this is extracted from context in the next block using linguistic and syntactic rules. By parsing each sentence, phrase and sentence level stress marks can be generated. These prosodic features are necessary to effect natural sounding speech.

The phonemic and prosodic string is then submitted to a processor to calculate control parameters for a dynamically controlled vocal tract model. The hardware implementation of this processor is the subject of this thesis. The last blocks in the figure include the vocal tract model, a digital-to-analog converter, a low pass filter, and finally an electro-mechanical speaker.

#### CHAPTER 2

#### Speech Synthesis by Rule -- The Klatt Model

The basic program for speech synthesis employed by the Natural Language Processing Group was developed by Dennis Klatt. The first step in the design of a hardware processor to implement his algorithms was careful examination of his code. Flowcharting two different versions of Klatt's code (the older one written in assembly language and FORTRAN for execution on a Digital Equipment Corp. PDP-9, the newer one written in PDP-10 FORTRAN) made clear certain frequently used procedures.

With the objective of an inexpensive, compact machine capable of performing the necessary computations in real-time, it is obvious that the architecture and instruction set of the processor must match closely the algorithmic tasks specified by the program. By isolating functions that occur frequently and providing for special hardware and software to execute these functions more efficiently, the processor speed has been maximized while minimizing memory requirements. The emphasis has been on maximizing the performance/cost ratio.

The next two sections briefly describe the vocal

tract model and its control strategy. The last section discusses the software and hardware design guidelines derived from Klatt's model.

#### 2.1 The Vocal Tract Model

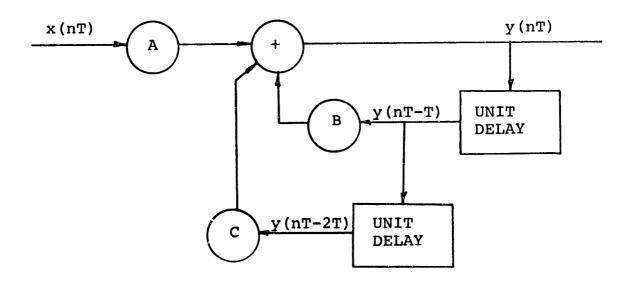

The Klatt model is based on the theory originated by Fant (Fant, 1960) that the transmission characteristics of the vocal tract are well approximated by a cascade of resonators (poles) and antiresonators (zeros) whose band-widths and center frequencies may be independently controlled. Speech can then be produced by dynamically altering the vocal tract resonances (formants) and supplying the necessary excitation source. The primary building block in Klatt's approach is a digital time-invariant linear filter, a device with transfer function comparable to an analog resonator. Two parameters, the frequency and the bandwidth, specify the input/output characteristics according to the second-order difference equation illustrated in Fig. 2.

$$y(nT) = A \cdot x(nT) + B \cdot y(nT-T) + C \cdot y(nT-2T)$$

where:

$$A = 1 - B - C$$

$B = 2 \cdot \exp[-\pi (BW) (T)] \cdot \cos[2\pi (F) (T)]$

$C = -\exp[-2\pi (BW) (T)]$

and n = sample number

BW = resonator bandwidth

T = period between samples

F = resonator frequency

x() = input sample

y() = output sample

Fig. 2 Difference equation to realize a digital resonator

A special piece of digital hardware is currently being constructed at MIT to implement this filter function. This device consists of a single high speed filter section that can be time multiplexed to effectively model all the resonators in Klatt's vocal tract model. Time multiplexing reduces the amount of hardware significantly: 1/n of the time the single high speed filter

simulates one of the n filters required by the Klatt model.

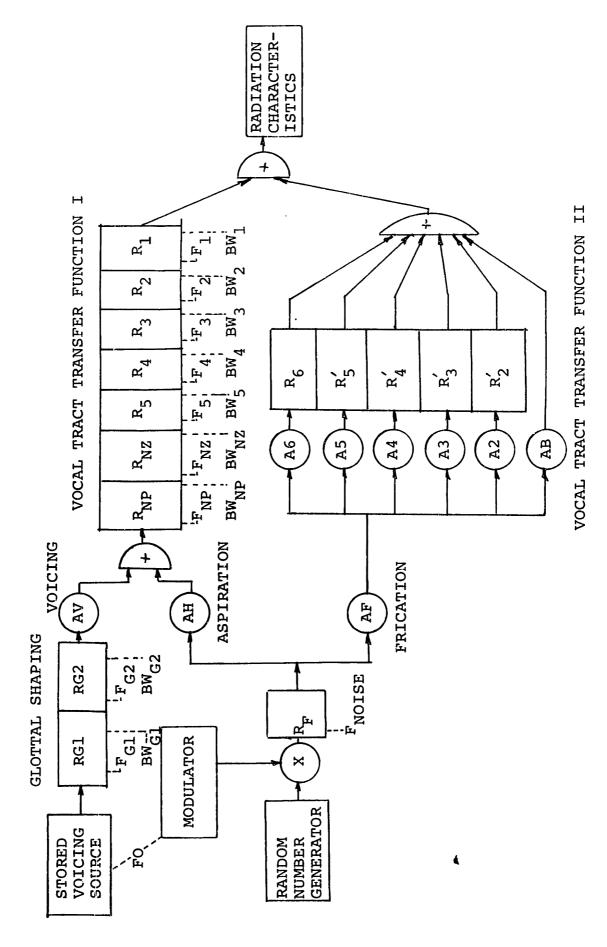

The model of the human vocal tract built from these digital filters is shown in Fig. 3. (Klatt, 1975) The input to the synthesizer is a set of 38 control parameters that are updated every five milliseconds, fast enough for the most rapid formant transitions. These parameters specify the resonant frequencies and bandwidths of the vocal cavity and the excitation applied to it.

The Klatt model provides for three separate excitation sources: voicing, aspiration, and frication. The voicing source is specified by the fundamental frequency (FØ), voicing amplitude (AV), break frequencies of a glottal shaping network ( $F_{Gl}$ ,  $F_{G2}$ ), and bandwidths of the glottal network ( $BW_{Gl}$ ,  $BW_{G2}$ ). FØ controls the frequency of an impulse generator which simulates the vocal cord vibrations. Aspirated sounds like "huh" and fricatives such as "sh" or "th" are caused by a turbulent air stream, and are modelled as white noise. Sources of aspiration and frication are derived from samples of a pseudo-random number generator which are passed through a low pass filter with cut-off frequency  $F_{NOISE}$ . There are independent controls for the amplitude of each (AH, AF).

The vocal tract transfer function for nasal and

Fig. 3 Vocal Tract Model (Klatt)

laryngeal sources is modelled by seven digital resonators connected in series with independent control parameters for the frequency and bandwidth of each filter. The first two resonators model nasal poles and zeros respectively. A separate transfer function for frication sources uses five digital formant resonators, each with its own amplitude control (A2-A6), in a parallel configuration. AB specifies the amplitude of the bypass path. Bandwidths for this section are calculated by multiplying the bandwidths, BW1-BW6 by a bandwidth scale factor (BWSCALE). This parallel (as opposed to serial) arrangement has been shown to better model fricatives.

To summarize, the control parameters are as follows:

| FØ                                 | fundamental frequency           |        |  |  |  |

|------------------------------------|---------------------------------|--------|--|--|--|

| F <sub>G1</sub> ,F <sub>G2</sub>   | glottal shaping network frequen | cies 2 |  |  |  |

| BW <sub>G1</sub> ,BW <sub>G2</sub> | " " bandwid                     | ths 2  |  |  |  |

| FNOISE                             | noise filter cut-off frequency  | 1      |  |  |  |

| AV                                 | amplitude of voicing            | 1      |  |  |  |

| АН                                 | " " aspiration                  | 1      |  |  |  |

| AF                                 | " " frication                   | 1      |  |  |  |

| AV <sub>MAX</sub>                  | maximum amplitude of voicing    | 1      |  |  |  |

| AH <sub>MAX</sub>                  | " " aspiration                  | 1      |  |  |  |

| AF <sub>MAX</sub>                  | " " frication                   | 1      |  |  |  |

| F <sub>NP</sub> , F <sub>NZ</sub>         | Nasal frequencies                      |    |  |  |

|-------------------------------------------|----------------------------------------|----|--|--|

| ${\tt BW}_{\tt NP}$ , ${\tt BW}_{\tt NZ}$ | " bandwidths                           | 2  |  |  |

| $F_1, \dots, F_6$                         | Vocal tract frequencies                | 6  |  |  |

| $BW_1, \dots, BW_6$                       | " " bandwidths                         | 6  |  |  |

| BW <sub>SCALE</sub>                       | bandwidth scale factor                 | 1  |  |  |

| AB                                        | Amplitude of bypass path               | 1  |  |  |

| A2,,A6                                    | Resonator amplitude controls           | 5  |  |  |

| ΔΤ                                        | period between input parameter updates | 1  |  |  |

| SAMP                                      | output sampling rate                   | 1  |  |  |

| NFRMT                                     | number of formants to be simulated     | 1  |  |  |

|                                           |                                        |    |  |  |

|                                           | Total                                  | 38 |  |  |

These 38 variables allow for extreme flexibility, however it is possible to set some to constant values. For example, all the bandwidths and the fourth, fifth, and sixth formant frequencies can be set to constants with only a small loss in speech quality. In doing so the number of control variables is reduced and the data rate necessary to drive the vocal tract model in real time is correspondingly reduced.

## 2.2 The Control Strategy

In the discussion thus far, the function of the control parameters has been described but no mention has

been made of the source of these parameters. The design and construction of a special purpose processor to produce these control parameters from an input string of phonemic and prosodic information demanded a careful study of Klatt's control algorithm.

Klatt's voice synthesis program takes a string of phonemes, stress markers, word boundaries, and syntactic brackets as input and computes parameter values for the vocal tract model. For each phoneme in the input string, an acoustic description is retrieved from a stored table. This phoneme dictionary contains constants such as typical duration, formant frequencies, and formant bandwidths for isolated phonemes. Information classifying the phonemes by feature (e.g. voiced, vowel, nasal, diphthong, ...) is also included in the dictionary. The program then calculates duration and pitch inflection based upon stress markers and syntactic brackets. interesting that duration rather than intensity of a vowel segment often determines which syllable is perceived as stressed. Phrase and sentence level stress markers determined from context are used in the generation of the pitch contours.

The next section of code uses a set of rules to compare features of adjacent phonemes and, based on their mutual effects, calculate formant transitions to

produce smooth, free flowing speech. The stored constants in the phoneme dictionary are treated as boundary values from which continuous parameter values are computed by interpolation.

## 2.3 Hardware and Software Implications

It cannot be overemphasized that the real-time computing capability and compact size necessitated a special purpose processor with a customized instruction set. Currently available low-cost minicomputers with general purpose instruction sets are simply too slow. Klatt's programs run ten to twenty times slower than real time on a DEC PDP-9. The speed and space constraints imply that in addition to a special instruction set, the computer must make use of parallel processing wherever cost-effective in order to improve the machine's cycle time. A strictly serial machine could be built but would require higher performance components at a much greater cost.

In all of Klatt's programs there is a large amount of array processing. Typically, the stored constants in the phoneme dictionary are accessed by a variable offset within a given array. The computed parameter values are also stored in an array with a similar data structure. A convenient method of implementing such a data structure

utilizes a base and index register: the address of the N<sup>th</sup> element of the array can be determined simply by adding the contents of the Base Register, START, (which is a pointer to the beginning of the array,) to the index register:

Fig. 4 Indexed Addressing of Arrays

Due to the high frequency of occurrence of this kind of data manipulation, it is desirable to provide for rapid indexed address calculation. Furthermore, the segment of code to implement this type of addressing should be concise to conserve instruction memory. This is discussed in detail in Chapter 3.

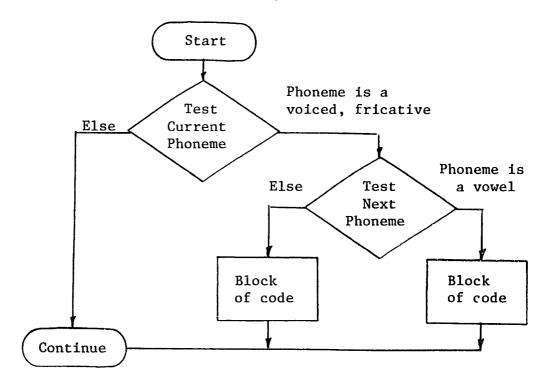

Phonemic feature testing is another type of process-

ing employed throughout Klatt's programs. Different blocks of code are executed depending upon the compared features of adjacent phonemes. A typical section of flowchart is shown below in Fig. 5:

Fig. 5 Section of flowchart exhibiting feature testing

This kind of testing can be conveniently implemented in the following way: a 40 bit data word is generated for each phoneme, each bit corresponding to a specific feature. Setting the bit to ONE means that the feature is present; ZERO means it is absent. Processing an input phoneme requires retrieving this feature word from the phoneme dictionary. Then, to perform a test for a

given feature, the feature word is logically ANDed bitby-bit with a mask containing all zeros except for the feature bits being tested. With this scheme it is easy to check for several features concurrently simply by setting the appropriate mask bits.

The frequent occurrence of this program structure motivated the development of two special instructions: Skip on Mask and Jump on Mask, which are described in detail in Chapter 3.

A significant amount of computation is involved in calculating the coefficients A, B, and C for the difference equation of Fig. 2. The derivation of the coefficients involves addition, subtraction, multiplication and the transcendental functions cosine and exponential. One of the countless number of hardware/software trade-offs that had to be made centered around which functions to include in the instruction repertoire and which ones to leave in the form of software subroutines. It was decided to include hardware and appropriate microcode for the arithmetic functions and leave the transcendental functions as subroutines. Among the factors influencing this decision were:

Addition, subtraction, and multiplication occur

often throughout the program. A hardware/firm ware multiply instruction has a small incremen-

tal cost and executes approximately ten times faster than a corresponding subroutine.

- 2. The cost of providing for transcendental functions in hardware is significant. If implemented in firmware, the microcode and its memory would double in size and price.

- 3. The important criterion in determining which functions should be sped up at the expense of increased complexity and cost is:

The execution time of e<sup>x</sup> and cosine is relatively unimportant since they account for less than 0.2% of the total number of instructions. A tenfold (1000%) increase in their execution speed would improve the overall performance of the machine by less than 2%.

4. Transcendental functions can be calculated with sufficient accuracy from the first three of four terms of a Taylor series or by interpolation in a table of stored values. Either method involves addition, subtraction, and multiplication. Thus the inclusion of the multiply in-

struction greatly enhances the execution speed for the transcendental functions.

Although not used as extensively as multiplication, a hardware/firmware divide has been included in the instruction set. Both multiplication and division are fixed point (vs. floating point) to minimize circuit and firmware complexity as well as execution time.

Keeping track of the location of the binary point is the programmer's responsibility. Since it may be necessary to scale numbers for multiplication and division, a single and double word shift instruction has been included.

For flexibility, a processor to handle speech synthesis programs should include some method for dealing with subroutines. Absence of recursion in the exising programs was partial justification for not using a stack architecture. An extensive discussion of the machine architecture will be found in Chapter 4.

The use of pointers and indirection, although not found in Klatt's code, will facilitate the handling of certain arrays. For example, to insert or delete an item from a list normally involves recopying part of the list. If one wanted to add the letter B to the following list, C, D, E, and F would have to be recopied into locations d, e, f, and g:

original list new list

| location | contents | location | contents |

|----------|----------|----------|----------|

| a        | A        | a        | A        |

| C        | С        | C        | В        |

| đ        | D        | d        | С        |

| е        | E        | e        | D        |

| f        | F        | f        | E        |

| g        |          | g        | F        |

Using pointers, only the pointer from location a would have to be changed and an entry created for B. The example given assumes the list is scanned from top to bottom:

original list new list

| location | data | pointer |

|----------|------|---------|

| a        | A    | c .     |

| С        | С    | d       |

| đ        | D    | е       |

| е        | E    | f       |

| f        | F    | -       |

| g        | -    | -       |

| location   | data | pointer |   |

|------------|------|---------|---|

| a          | A    | b       |   |

| С          | C    | đ       | 1 |

| đ          | D    | е       |   |

| e          | E    | f       |   |

| , <b>f</b> | F    | _       | 1 |

| b          | В    | С       | F |

The input/output requirements of Klatt's control program have certain implications for the design of a special purpose processor. The only input is a phonemic transcription of printed text from an external computer; the only outputs are the coefficients and parameters transmitted to a third device, the vocal tract model. Although a bidirectional I/O bus could have been used to communicate with the other machines, separate input and output buffers simplify the design and are better suited to the task.

Furthermore, an interrupt system is not necessary.

If the machine is ready for the next phoneme but the input buffer is empty there is no processing required until the next phoneme is delivered. The machine simply enters a wait cycle until new data is entered into the buffer.

For output the situation is similar: once the 38 parameters are ready the processor dumps them into the output buffer as fast as possible. A small, high speed memory reads the parameters from the output buffer and stores them for 5 msec. for the vocal tract model. A special instruction, OUTPUT, has been devised to transmit all the coefficients at a rate exceeding two million/second.

At a later date, when the entire processor can be reduced to several chips, the program will be stored in a nonvolatile memory (i.e. Read Only Memory -- ROM), so that the program remains intact even when the power is turned off. A separate read/write memory will still be needed, however, to store all the variables. Keeping this in mind now, the processor has separate program and data memories. Separate memories are actually an asset, since they allow for concurrent referencing and therefore faster processing.

Further details of the actual instruction set and computer architecture design that were dictated by Klatt's algorithm follow in Chapters 3 and 4.

#### CHAPTER 3

#### Instruction Set Design

After studying Klatt's algorithms, the next step in the design of the processor was the development of the instruction repertoire. The issues of instruction encoding, the number of different instructions, the precision of the data representation, and the size of the memory all influenced the detailed design of the instruction set. An instruction word that is too short in length limits the bits available for the operational code (OP code) and/or the operand address, and can severely restrict the machine's computational power. On the other hand, an instruction that is too long is more powerful but wastes valuable memory space. A well chosen instruction length allows several shorter instructions to be combined into one and can increase processor speed by reducing the number of instruction fetches from memory. By tailoring the instruction set to the particular task, a compromise can be reached that maximizes the computing power and flexibility of each instruction, while minimizing memory requirements. In addition, if the instructions reflect the structure of the underlying algorithms, programs will be easier to write, debug,

modify, and comprehend.

In general, most instructions need five pieces of information:

- 1. OP code, i.e. the function to be performed

- 2. The location of the first operand

- 3. The location of the second operand

- 4. The location for deposit of the resultant

- 5. The location of the next instruction

Different machines can be designed depending on whether

these data are explicitly or implicitly defined. In a

4-address machine all four addresses, in addition to

the OP code, are specified by the programmer. The inherent wide instruction word provides a flexibility

rarely needed at a high cost in memory. A 3-address

machine assumes the program will be executed sequentially

except for jump and skip, and thereby eliminates the

next instruction field. The next logical step in shortening the instruction is the 2-address machine which

performs the function on the two specified operands

and deposits the result in the location of one of the

operands (i.e. A + B + B).

The most common addressing scheme, especially among minicomputers, is single addressing. Operations are performed on the specified operand and an implicit register called the accumulator (AC). The resultant is

deposited in the accumulator (i.e. AC + B → AC). A zero-address machine, sometimes called a stack machine, has all addresses defined implicitly. The next instruction is maintained in a program counter, the two operands are the top two cells of a pushdown stack, and the result is returned to the top cell of the stack. Stack machines are particularly good for arithmetic processing where equations are expressed in reverse Polish notation, and for machines with a heavy reliance on recursion.

By writing parts of Klatt's code for each of these machines and by comparing their hardware implementation costs, the 2-address format was chosen as a reasonable compromise with relatively good coding efficiency. Within the specific context of Klatt's algorithm: the 4-address machine is too general and therefore inefficient; there are not enough skips and jumps to justify a 3-address machine; as shown below the single address machine requires more instructions; finally a stack machine is unjustified due to the inefficiency in addressing registers low in the stack, and since the program makes little use of recursion.

Multiple high-speed registers within the CPU reduce the amount of data movement, save macroinstructions, and reduce the number of references to memory. A program for a single address machine which adds the contents of location A and location B and deposits the result in location B is shown below:

| memory : | re | fe | ren | ce |

|----------|----|----|-----|----|

|----------|----|----|-----|----|

Accumulator (AC) + loc A yes

-

$AC \leftarrow AC + loc B$

yes

AC + loc B

yes

By having a large number of registers, the program can be written to increase the likelihood that the contents of location A and location B already have been fetched from memory and reside in one of the high speed internal registers. If this is the case, the above code can be reduced to a single line without any memory references:

Register B + Register A + Register B

In the speech processor, register-to-register instructions utilize the high-speed registers and can operate almost twice as fast as those that reference memory.

The computer's CPU includes 17 internal registers:

- a. Register O (microprocessor buffer register -Reg. MB) is invisible to the user. It is used

for temporary storage by the microcode.

- b. Register 1 is a dedicated program counter (PC).

- c. Registers 2-7 are reserved as index or base registers. They are especially useful in array addressing and table look-up.

- d. Registers 8-15 are general purpose working registers.

- e. Register "Q" is invisible to the user and is used by the microcode in multiplication, division, and shifting.

## 3.1 Memory Reference Instructions-Address Calculation

Throughout this chapter the following symbols are used:

- ( ) refers to the contents of the memory location or register enclosed in parentheses

- "is transferred to"

- logical AND

U - logical OR

- one's complement

Reg.- register

Reg. D - destination register

E - effective address

I - indirection

MSB - most significant bit

LSB - least significant bit

LABEL: - the colon indicates the variable to

the left is a label corresponding

to the address of that location

S - sign bit

Each memory reference instruction includes information necessary to calculate the absolute address from which data is stored or fetched. Addressing information is contained in three distinct fields occupying bits 0-11. Bits 0-7 are the displacement, 8-10 the base register bits, and bit 11 the indirect bit.

| 11 | 10  | 9           | 8 | 7 | 6   | 5     | 4     | 3_ | 2 | 1 | <u> 0 B</u> IT # |

|----|-----|-------------|---|---|-----|-------|-------|----|---|---|------------------|

| I  | BAS | SE<br>GISTE | R |   | DIS | PLACI | EMEN' | Г  |   |   |                  |

The displacement is an 8 bit signed number in two's complement notation with an octal range of -200 to +177. When the base register specified is non-zero, base addressing occurs; the displacement is added to the contents of the base register to generate a memory address. If the base register is  $001_2$ , the program counter is chosen. This provides for relative addressing, a feature especially useful in altering the normal program sequence by jumping relative to the location of the

current instruction. The programmer should note that due to instruction overlap fetching, the PC points two locations beyond the current instruction. When the base register bits are  $000_2$ , rather than adding the displacement to Reg. O, the displacement is treated as an absolute address with a range of  $000-377_8$ .

If the indirect bit is 0, the effective address has already been calculated from the base register and displacement bits. However, when the indirect bit is 1, addressing is indirect and the machine retrieves another address from the location of the address already specified. There is only one level of indirection.

Indirection is desirable especially in programs using pointers. After reviewing Klatt's program, it became clear that pointers and indirection could simplify the handling of data. In a sequence requiring indirect addressing, an instruction capable of indirection can replace two normal instructions, thereby saving memory and increasing execution speed.

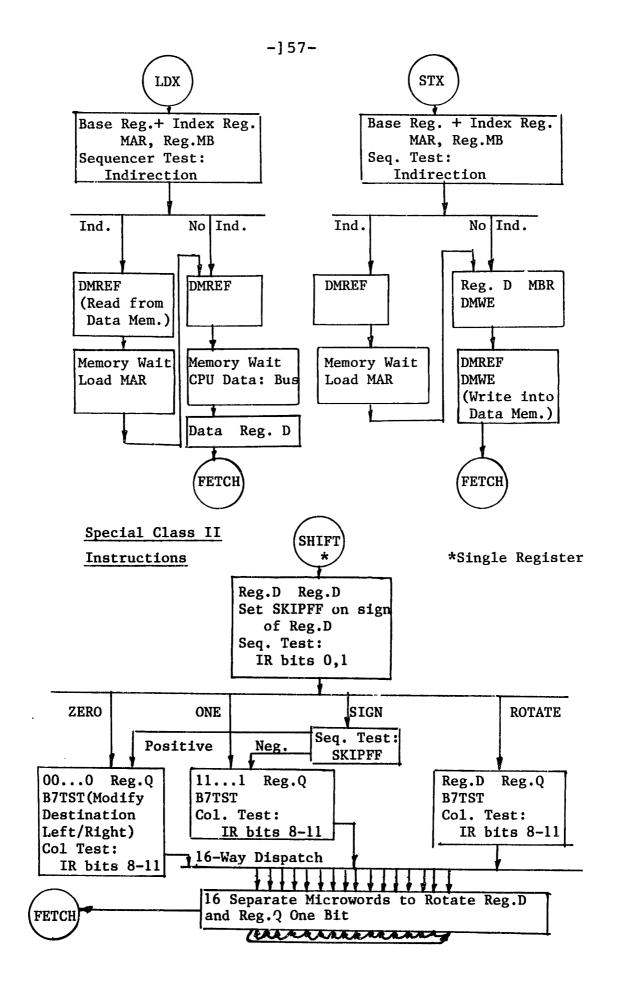

Another type of memory reference instructions was included to handle the accessing of variable entries within a list. These instruction, LDX and STX are described in section 3.3.

# 3.2 Single OP Code (Class I) Instruction

Class I instructions have a 4 bit OP code, usually reference memory, and follow the general pattern shown below:

| BIT # | 19 18 17 16 | 15 14 13 12 | 11 | 10 9 8 | 7 6 5 4 3 2 1 0 |

|-------|-------------|-------------|----|--------|-----------------|

|       | OP Code     | Reg. D      | Ι  | Base   | Displacement    |

|       |             |             |    | Reg.   |                 |

A summary of all instruction mnemonics and formats, including the various modifier fields is given in Appendix C.

| OP Code | Function<br>Mnemonic | Explanation                           |  |  |  |  |  |  |  |  |

|---------|----------------------|---------------------------------------|--|--|--|--|--|--|--|--|

| 008     | ADD                  | To summarize the calculation of       |  |  |  |  |  |  |  |  |

| -       |                      | the effective address E from          |  |  |  |  |  |  |  |  |

|         |                      | bits 0-11:                            |  |  |  |  |  |  |  |  |

|         |                      | if the Base Reg $\neq$ 0 and          |  |  |  |  |  |  |  |  |

|         |                      | $I=0$ then $E=\{(Base\ Reg)+Signed\}$ |  |  |  |  |  |  |  |  |

|         |                      | Displacement                          |  |  |  |  |  |  |  |  |

|         |                      | or                                    |  |  |  |  |  |  |  |  |

|         |                      | \ LABEL \                             |  |  |  |  |  |  |  |  |

|         |                      | I=1 then $E=\int ((Base Reg)+Signed)$ |  |  |  |  |  |  |  |  |

|         |                      | Displacement)                         |  |  |  |  |  |  |  |  |

|         |                      | or                                    |  |  |  |  |  |  |  |  |

|         |                      | (LABEL)                               |  |  |  |  |  |  |  |  |

|         |                      | if the Base Reg $= 0$ and             |  |  |  |  |  |  |  |  |

|         |                      | I=0 then E= Positive displacement     |  |  |  |  |  |  |  |  |

|         |                      | or                                    |  |  |  |  |  |  |  |  |

|         |                      | \ LABEL \                             |  |  |  |  |  |  |  |  |

| <b>I=1</b> | then | E= | (Positive | displacement) |

|------------|------|----|-----------|---------------|

|            |      |    |           | or            |

|            |      | į  | (1        | LABEL)        |

The contents of this address are added to the D register (one of the 15 internal registers). The D register also serves as the destination register. All data are in 2's complement notation. Using the above notation:

$(E) + (Reg.D) \rightarrow (Reg. D)$

(E) -  $(Reg. D) \rightarrow (Reg. D)$

$(E) \cup (Reg. D) \rightarrow (Reg. D)$

$(E) \cap (Reg. D) \rightarrow (Reg. D)$

$(E) \rightarrow (Reg. D)$

$(Reg. D) \rightarrow (E)$

Increment Skip if Zero. The first step is  $(E)+1 \rightarrow (E)$ . If the final result equals zero, the program counter (PC) is incremented to cause the subsequent instruction to be skipped. The D register field is not used. Additional hardware could use these 4 bits as a modifier field to create more instructions. Presently, the increased complexity was considered unnecessary.

07<sub>8</sub> SDC

018

028

038

048

05<sub>8</sub>

06<sub>8</sub>

SUB

OR

AND

LOAD

STORE

ISZ

Skip if Different Contents. If

(E)≠(Reg. D), the next instruction

is skipped. The next instruction is

executed normally if the two operands

are equal. In both cases the contents

10<sub>8</sub> SM

of E and Reg. D remain unchanged.

Skip on Mask. The complement of (E),

(E) is bit-by-bit logically ANDed with

(Reg. D). The result is not deposited

or stored, however the next instruction

is skipped if all the resultant bits

equal zero. In other words a skip occurs

when:

$$[\overline{(E_0)} \cap (\text{Reg. } D_0)] \cup [\overline{(E_1)} \cap (\text{Reg. } D_1)] \cup \dots$$

$$[\overline{(E_{15})} \cap (\text{Reg. } D_{15})] = 0$$

where the subscripts refer to the bit being tested.

This function has applications in feature testing, a technique used extensively in speech synthesis programs. Suppose in Reg. D each bit represents a feature such as voiced, nasal, fricative, etc. Setting a bit to 1 means the feature is present. For example, part of the code for a voiced, fricative phoneme may look as follows:

VOICED NASAL FRIC. SONORANT Reg. D 1 0 1 0

If one wanted to test the phoneme to determine whether it is voiced, the following mask would be used.

$$\overline{E}$$

1 0 0 0 0 to produce  $\overline{(E)}\eta$  (Reg. D) 1 0 0 0

Since all bits are not equal to zero, the next instruction is executed. Now if the

same phoneme undergoes a nasal test the

mask:

$\overline{\mathbf{E}}$  0 1 0 0 produces 0 0 0 0

and the next instruction is skipped since the phoneme is not nasal. To summarize, the subsequent instruction is skipped if the feature tested is not present.

It is possible to test more than one feature at a time. To test whether a phoneme is "voiced OR fricative", in this example one would use the mask:

1 0 1 0

causing the next instruction N to be executed.

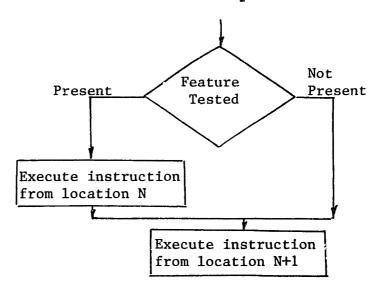

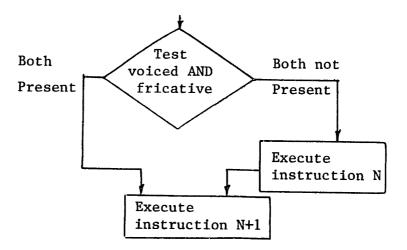

Testing for "voiced AND fricative" involves including one bit in Reg. D for voiced and another for fricative. The actual test performed, "voiced OR fricative" is logically equivalent to "voiced NAND fricative". In this example, the features tested (voiced OR fricative) are not present so the instruction N+1 is executed. Given the function NAND, AND can be realized by reversing the roles of the two possible branches as shown below.

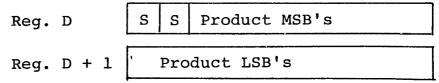

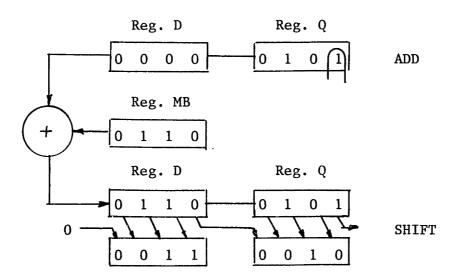

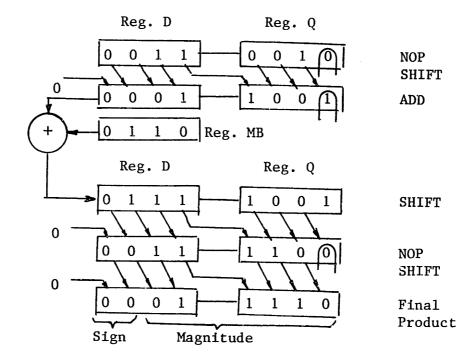

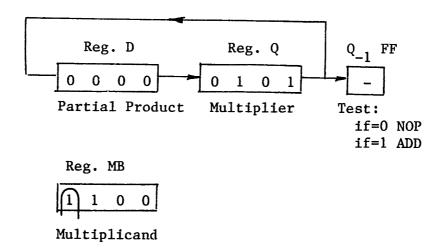

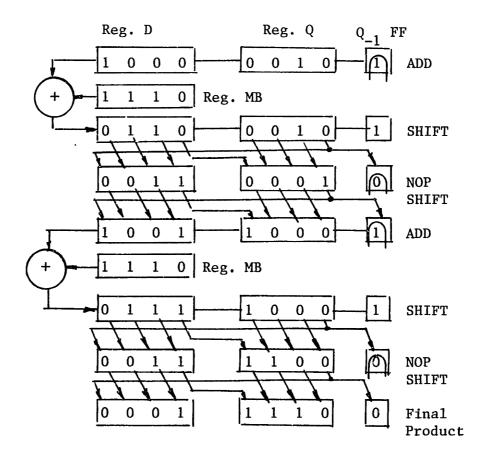

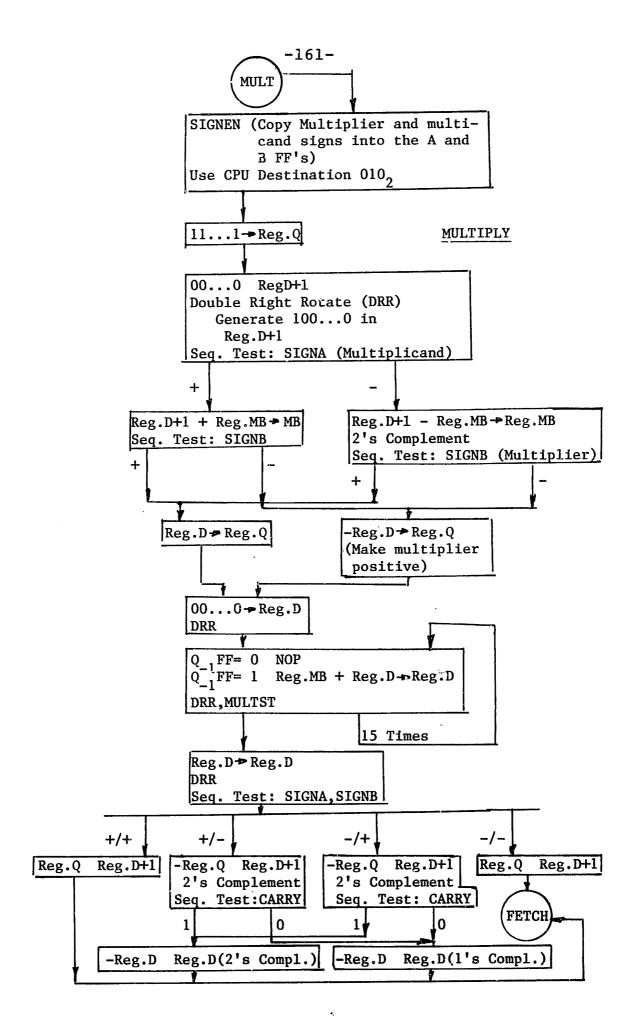

MULT Multiply the signed numbers (E) and (Reg. D) to generate a double length product. The higher order bits of the product are found in Reg. D and the lower order bits are found in Reg. D+1. Reg. D must be located on an even boundary (i.e. must be an even register). A few extra logic elements together with clever microprogramming provides for a 16x16 bit signed multiplication in slightly over 3 microseconds.

In performing signed multiplication of 16 bit numbers (1 sign bit and 15 magnitude bits), the magnitude of the product is 30

instead of 31 bits long. The actual algorithm used produces two equal sign bits in the two MSB's of Reg. D (bits 14, 15) corresponding to the sign of the product

$(E) \times (Reg. D) \rightarrow (Reg. D, Reg. D+1)$

Final conditions:

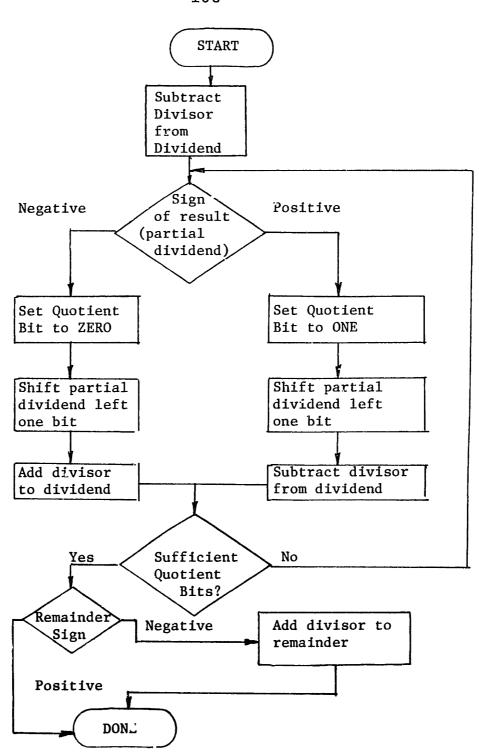

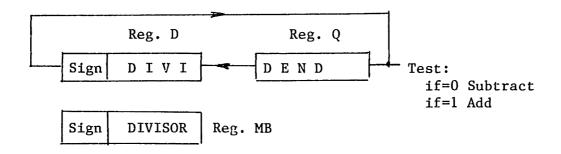

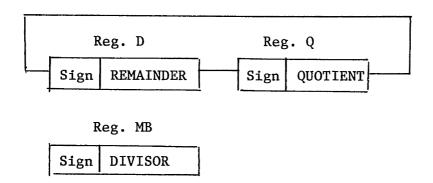

12<sub>Q</sub> DIV

Initially the double length dividend is found in Reg. D (high order bits) and Reg. D+1 (low order bits). The divisor is found in (E).

Initial conditions:

| Reg. D   | S | S Dividend MSB's (15 bits) |                      |  |  |  |  |  |  |

|----------|---|----------------------------|----------------------|--|--|--|--|--|--|

| Reg. D+1 | D | ividend LSB's<br>(15 bits) | Don't<br>Care(l bit) |  |  |  |  |  |  |

| Loc. E   | s | Divisor (15 b              | its)                 |  |  |  |  |  |  |

By convention, the absolute value of the dividend must be smaller than the absolute value of the divisor to prevent overflow.

Before the division is performed a test for overflow, if affirmative sets the OVERFLOW Flag. As in all arithmetic operations, the programmer must keep track of the binary point. For certain operations it may be necessary to scale operands to maintain enough significant bits.

After the division is complete, Reg. D contains the 16 bit quotient. The signs are as follows:

| Original<br>Dividend |   | iginal<br>visor | Remainder | Quotient |

|----------------------|---|-----------------|-----------|----------|

| +                    |   | +               | +         | +        |

| +                    |   | -               | +         | -        |

| -                    |   | +               | -         | -        |

| -                    |   | -               | -         | +        |

| Finally:             |   |                 |           |          |

| Reg. D               | s | Rema            | inder     | ]        |

| Reg. D+1             | S | Quot            |           |          |

| Loc. E               | s | Divi            | ]         |          |

Once again Reg. D must be an even register.

13<sub>8</sub> JMP(JSR) Jump-Jump to Subroutine. There are two kinds of jumps depending upon whether Reg. D=0000. When Reg. D≠0000, the address of the next instruction (PC+1) is first stored in Reg. D and then the subroutine's starting address is placed into the PC. This provides for a simple yet effective means of jumping to and returning from subroutines. If Reg. D=0000 the PC is not saved and an ordinary unconditional jump is performed. In both cases the effective address is computed and specifies the address of the next instruction to be executed.

To summarize the effects of

If Reg. D = 0000 then E

$$\rightarrow$$

(PC)

If Reg. D  $\neq$  0000 then (PC)+1  $\rightarrow$  (Reg. D)

E  $\rightarrow$  (PC)

In the following example, when the first JMP instruction is encountered, the return address NEXT is saved in Reg. 11 and the subroutine is then executed:

NEXT:

•

SUBROUTINE:

JMP 0.11.0 E=(Reg. 11)=NEXT $\rightarrow$ (PC)

At the conclusion of the subroutine, by jumping to the address contained in Reg. 11, program execution continues at location NEXT. If many subroutines are being used or there is a shortage of working registers, the return may be stored in a temporary location as shown below:

SUBROUTINE: STORE 11, TEMP (Reg.11) = NEXT >

(E) = (TEMP)

JMP INDIRECT 0, TEMP

E = (TEMP) = NEXT >

(PC)

TEMP: NEXT

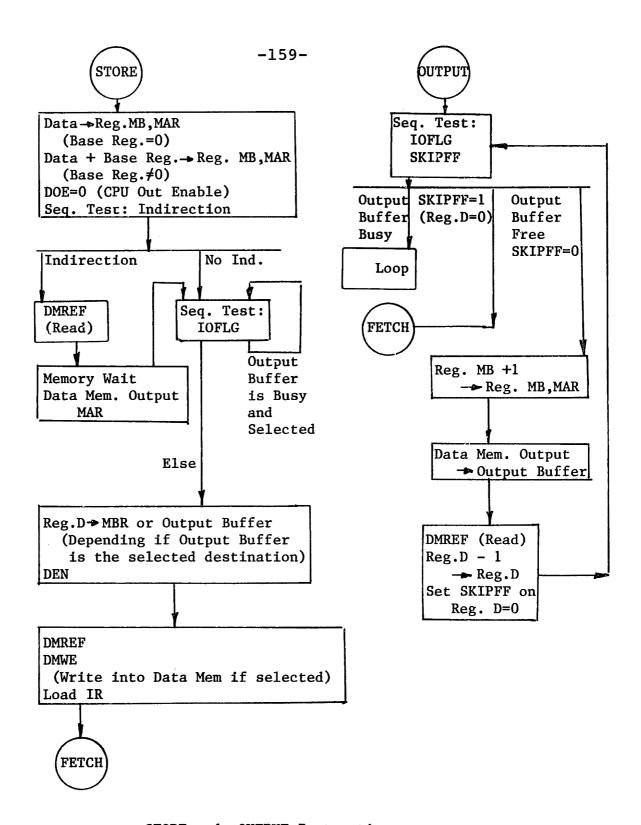

14<sub>8</sub> OUTPUT

This special instruction provides for easy, rapid transfer of blocks of data from the data memory to the output buffer. E specifies the first word and (Reg. D) contains the number of adjacent words to be transferred out. With OUTPUT, somewhere between 1-2 million words/second can be moved directly from the memory to the output buffer without passing through the CPU. Comparing codes for outputting data:

## Using OUTPUT

LOAD 8, THIRTY8 (E) = (THIRTY8) = 38 + (Reg. 8)

OUTPUT 8, START

:

THIRTY8: 38<sub>10</sub> # of words to be transferred START: STARTADR Starting address

## Conventional

LOAD 7, NTHIRTY8 (E) = (NTHIRTY8) = -38 + (Reg. 7)

LOAD 6, END (END) = LASTWRD + (Reg. 6)

BACK: LDX 9,6,7 ((Reg. 7) + (Reg. 6)) + (Reg. 9)

STORE 9, OUTPUT (Reg. 9) + OUTPUT Buffer

INCZ 7 (Reg. 7) + 1 + (Reg. 7) and skip

on zero.

JMP 0,BACK E=BACK→(PC) (e.g. loop 38 times)

:

NTHIRTY8: -38<sub>10</sub>

END: LASTWRD Location of last word

In Klatt's program, it is necessary to output 38 parameters every 5 milliseconds. The OUTPUT instruction operates approximately

5 times faster than conventional code and saves 20 milliseconds of computing time for every second. The 2% reduction in overall execution time does not require extra hardware, only microcode. The OUTPUT instruction is a useful feature to have, but is not essential. Its utility should be reviewed as new algorithms and programs for speech synthesis are developed.

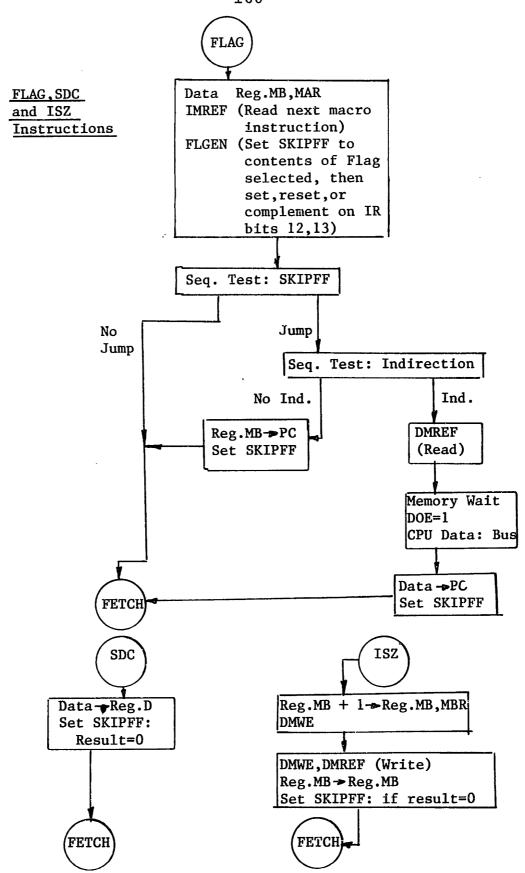

15<sub>8</sub> FLAG The FLAG instruction has a special format:

The device selcts one of the eight status flip-flops.

| Bit | 10 | 9 | 8  |          |

|-----|----|---|----|----------|

|     | 0  | 0 | 0  | OVERFLOW |

|     | 0  | 0 | 1  | RUN      |

|     | 0  | 1 | 0  | CARRY    |

|     | 0  | 1 | 1  | IN       |

|     | 1  | 0 | 0  | OUT      |

|     | 1  | 0 | 1. | Xl       |

|     | 1  | 1 | 0  | / X2     |

|     | 1  | 1 | 1  | х3       |

Bits 14,15 cause a conditional jump based on the state of the selected flip-flop.

| Bit | 15 | 14 | - |    |      | Mnemonic |

|-----|----|----|---|----|------|----------|

|     | 0  | 0  |   | ЙO | Jump | -        |

|     | 0  | 1  |   | 11 | 11   | _        |

| Bit | 15 | 14 | - |      |    | $\overline{b}$ | Inemonic |

|-----|----|----|---|------|----|----------------|----------|

|     | 1  | 0  |   | Jump | on | flip-flop=0    | Z(ero)   |

|     | 1  | 1  |   | Jump | on | flip-flop=1    | 0(ne)    |

The address jumped to is restricted to locations 0-377<sub>8</sub> unless indirection is used. With indirection, any address in the memory can be accessed through these locations.

After the jump test has been performed, regardless of whether a jump actually occurred, the selected flip-flop can be set, reset or complemented according to bits 12,13.

| <u>Bit</u> | 13 | 12 | (Mnemonic)              |       |  |  |  |  |  |  |

|------------|----|----|-------------------------|-------|--|--|--|--|--|--|

|            | 0  | 0  | Flip-Flop (FF) unchange | d (-) |  |  |  |  |  |  |

|            | 0  | 1  | Reset FF to 0 (R)       |       |  |  |  |  |  |  |

|            | 1  | 0  | Set FF to l (S)         |       |  |  |  |  |  |  |

|            | 1  | 1  | Complement FF (C)       |       |  |  |  |  |  |  |

The machine can be HALTed by resetting the RUN flip-flop, in which case the computer waits until the FF is set by an external switch.

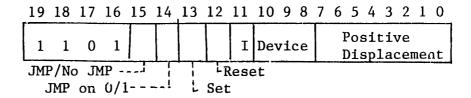

16<sub>8</sub> JM Jump on Mask. Special instruction well suited for testing the state of individual bits within a 16 bit word. This function is particularly useful in feature testing. The format is:

| 19 | 9          | 18 | 17 | 16 | 15      | 14         | 13  | 12 | 11 | 10                | 9 | 8 | 7 | 6 | 5         | 4        | 3   | 2   | 1   | 0  |

|----|------------|----|----|----|---------|------------|-----|----|----|-------------------|---|---|---|---|-----------|----------|-----|-----|-----|----|

|    | l          | 1  | 1  | 0  | D<br>Ma | Fie<br>ask | eld |    |    | Reg<br>Und<br>Tes |   | r | S | I | P(<br>Dis | С<br>sp: | Lac | cer | nei | nt |

|    | JMP on 0/1 |    |    |    |         |            |     |    |    |                   |   |   |   |   |           |          |     |     |     |    |

The register whose bits are to be tested is specified with bits 8-10. The D field in this case does not represent a register, but specifies which bit should be tested. Bit 11 determines whether to jump when the tested bit equals 0 or 1. As an example, the instruction to jump back 25 locations relative to the PC (recalling that the PC always points two locations beyond the current instruction) when bit #3 of base register 5 equals 1 would be as follows:

## With JM

| OP Cod | e Mask | JMP on | Reg. | Displacement                              |  |  |  |  |  |  |

|--------|--------|--------|------|-------------------------------------------|--|--|--|--|--|--|

| 1110   | 0011   | 1      | 101  | -27 <sub>10</sub> = 110 0101 <sub>2</sub> |  |  |  |  |  |  |

## Convential Code

LOAD 8, MASK (E)=(MASK) $\rightarrow$ (Reg. 8) ANDZ 8,5 (Reg. 5) $\land$ (Reg. 8) $\rightarrow$ (Reg. 8) and skip if result=0

JMP 0,1,  $-27_{10}$  E=(PC) $-27_{10}$  +(PC)

:

MASK: 0000 0000 0000 1000

If bit #3 equals 0, the jump does not occur and the next instruction is executed. When compared to conventional code, JM saves one memory reference (this is important since the memory is relatively slow), saves instruction memory by replacing 3 instructions with one and saves data memory by eliminating storage of the masks. The JM instruction also

operates almost 3 times faster than the conventional code. In Klatt's code, as it currently stands, JM implies a potential saving on the order of 500 macroinstructions together with higher speed.

17<sub>8</sub> Class II Dispatch This OP code causes the computer to find the required operation from the FUNC field (bits 4-7). This simple form of variable length coding makes efficient use of the instruction word.

In most instructions the destination is a register and can be represented by 4 bits. The source in Class II instructions, however, is a register (again 4 bits), whereas in Class I instructions it is an effective memory address requiring 12 bits. possible to break the instruction into shorter words, but the additional number of memory fetches would slow the machine substantially. The disparity in instruction size is handled by using a 4 bit OP code for Class I instructions and 8 bits (OP code-4 bits, FUNC code-4 bits) plus a 4 bit modifier field for Class II instructions.

# 3.3 Class II Instructions

With the exception of LDX and STX, Class II instructions involve register to register operations. All Class II instructions have the OP code llll<sub>2</sub> which enables another 4 bit field, called the FUNC field. The FUNC field is decoded to represent an additional 16 instructions. Most Class II instructions follow this format:

| 19 | 18 | 17 | 16 | 15 | 14  | 13 | 12 | 11 | 10  | 9 | 8 | 7 | 6          | 5 | 4 | 3  | 2   | 1 | 0    |     |

|----|----|----|----|----|-----|----|----|----|-----|---|---|---|------------|---|---|----|-----|---|------|-----|

| 1  | 1  | 1  | 1  | Re | eg. | D  |    | Re | ≘g. | A |   |   | FUN<br>Coc |   |   |    | >   | = | <    |     |

|    |    |    |    |    |     |    |    |    |     |   |   |   |            |   |   | De | epo | s | it I | Bit |

All Class II instructions except SHIFT, LDX and STX contain a four bit modifier field in bits 0-3.

Bits 0-2 cause the next instruction to be skipped if the condition is met.

| Bit 2 | 1 | 0 | Skip if result | Mnemonic |

|-------|---|---|----------------|----------|

| 0     | 0 | 0 | Never          | -        |

| 0     | 0 | 1 | <0             | LT       |

| 0     | 1 | 0 | =0             | Z        |

| 0     | 1 | 1 | <=0            | LE       |

| 1     | 0 | 0 | >0             | GT       |

| 1     | 0 | 1 | <b>≠</b> 0     | NE       |

| Bit 2 | 1 | 0 | Skip if result | Mnemonic |

|-------|---|---|----------------|----------|

| 1.    | 1 | 0 | >=0            | GE       |

| 1     | 1 | 1 | Always         | A        |

## Mnemonic

Bit 3 = 1 - The result is deposited in the destination register.

= 0 # The result is not deposited. This feature allows testing without

affecting either source register.

| FUNC Code       | Function<br>Mnemonic | Explanation                                                                |

|-----------------|----------------------|----------------------------------------------------------------------------|

| 008             | ADD                  | $(Reg.A) + (Reg.D) \rightarrow (Reg.D)$                                    |

| 018             | SUB                  | (Reg.D) - (Reg.A) + (Reg.D)                                                |

| 028             | OR                   | $(Reg.A)U(Reg.D) \rightarrow (Reg.D)$                                      |

| 038             | AND                  | $(Reg.A) \cap (Reg.D) \rightarrow (Reg.D)$                                 |

| 048             | MASK                 | $\overline{(\text{Reg.A})} \cap (\text{Reg.D}) \rightarrow (\text{Reg.D})$ |

| 05 <sub>8</sub> | MOV                  | $(Reg.A) \rightarrow (Reg.D)$                                              |

| 068             | INC                  | $(Reg.D)+1 \rightarrow (Reg.D)$                                            |

| 078             | DEC                  | $(Reg.D)-1 \rightarrow (Reg.D)$                                            |

| 108             | COM                  | One's complement. $(Reg.D) \rightarrow (Reg.D)$                            |

| 118             | NEG                  | Two's complement. $(Reg.D)+1 \rightarrow (Reg.D)$                          |

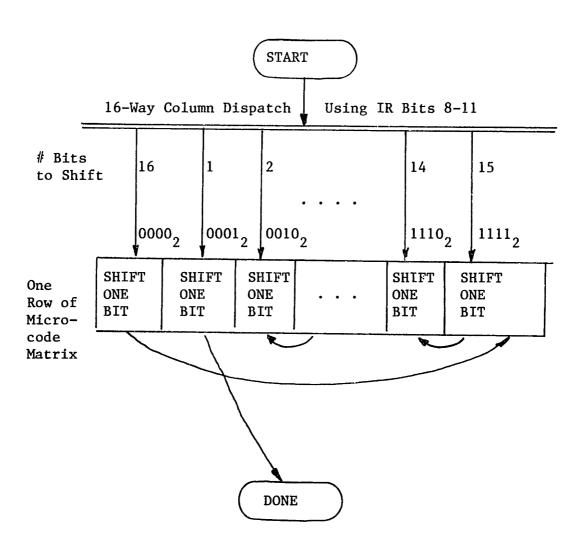

| 128             | SHIFT                | The format for SHIFT is slightly                                           |

|                 |                      | different from the standard:                                               |

Bit 3

| IR Bit# | 3              | 2                 | 1              | 0                 |  |

|---------|----------------|-------------------|----------------|-------------------|--|

|         | Right/<br>Left | Double/<br>Single | Shift<br>0,1,S | in:<br>ign,Rotate |  |

Bits 0-3 are a modifier field to provide for all combinations of shifts and rotates. The A field is interpreted as a literal and specifies the number of bits to be shifted.

Mnemonic

| 1     | R        | Right shift or      |

|-------|----------|---------------------|

|       |          | rotate              |

| 0     | L        | Left shift or       |

|       |          | rotate              |

| Bit 2 | Mnemonic |                     |

| 0     | S        | Single word (Reg.D) |

| 1     | D        | Double word. Reg.D- |

|       |          | higher order bits   |

|       |          | Reg.D+1-lower order |

|       |          | bits                |

|       |          | Reg.D must be on    |

|       |          | an even boundary.   |

| Bit | 1 | 0 | Mnemonic |    |     |    |       |      |      |       |

|-----|---|---|----------|----|-----|----|-------|------|------|-------|

|     | 0 | 0 | Z        | Sh | ift | in | zer   | os   |      |       |

|     | 0 | 1 | 0        | 11 | ti  | 11 | one   | 3    |      |       |

|     | 1 | 0 | s        | ** | Ħ   | ** | the   | sig  | n of | Reg.D |

|     |   |   |          |    |     | (0 | if Re | eg.D | is   | (+)   |

|     |   |   |          |    |     | 1  | 11    | **   | **   | (-))  |

1 1 R Rotate

Example: Double shift Reg.10 and Reg.11 to the right 5 places and fill the vacant bits with zeros (SHIFTRDZ).

OP code Reg.D Reg.A FUNC Modifier 1111 1010 0101 1100 01.00

138 LDX Load Indexed. LDX and STX use the format:

| 19 | 18 | 17 | 16 | 15 | 14  | 13 | 12 | 11 | 10       | 9   | 8 | 7 | 6   | 5  | 4 | 3        | 2   | 1 | 0 |

|----|----|----|----|----|-----|----|----|----|----------|-----|---|---|-----|----|---|----------|-----|---|---|

| 1  | 1  | 1  | 1  | Re | ≥g• | D  |    | I  | Ba<br>Re | ase |   | ] | FUI | VC |   | Ir<br>Re | ıde | × |   |

Normally the code to access the n<sup>th</sup> entry of a table starting at memory location TBSTRT would be as follows:

Assume initially:

(Reg.7) = N

(Reg.8) = TBSTRT

and that the contents of these registers must be maintained.

$TBSTRT) = DATA \rightarrow (Reg. 10)$

:

TBSTRT:

•

### TBSTRT+N DATA

The LDX and STX instructions, in addition to including indirection, a destination register and a base register, also have an index register. The effective address is equal to the sum of the contents of the base register and the contents of the index register. The code for the above example now is reduced from three lines to one:

The high frequency of this kind of memory reference in Klatt's program was a strong motivation for its inclusion in the instruction set. Several hundred instruction memory locations are saved with a corresponding decrease in execution time.

### LDX

```

I=0 ((Base Reg.)+(Index Reg.))→(Reg.D)

```

I=1  $(((Base Reg.)+(Index Reg.))) \rightarrow (Reg.D)$

# 148 STX Store Indexed.

```

I=0 (Reg.D) + ((Base Reg.) + (Index Reg.))

```

I=1 (Reg.D)→(((Base Reg.)+(Index Reg.)))

158-178

These FUNC codes are currently vacant and allow room for new instructions.

#### 3.4 Status Flags

OVERFLOW Set if the result of previous operation resulted in an arithmetic overflow. Reset with FLAG instruction.

Set externally to start the machine. Can RUN be reset under program control to halt the machine.

Set by the previous operation if the CARRY operation caused a carry out of its most significant bit. CARRY is useful for double precision arithmetic.

IN Set by external device when contents of input buffer is valid. When program requests data from the input buffer, the flag is tested. Data is transferred only if the IN flag is set (valid input). Ιf not set, the program will wait. flag is reset after data transferral.

OUT Set when contents of output buffer has been transferred to an external device and therefore the buffer is free.

is tested when output buffer is requested. Data is transferred from the common bus to the buffer only if the OUT flag is set. Program will wait if the buffer is already full. The flag is reset after the buffer is filled.

Controls the write enable line of the instruction memory.

instruction memory.

X2,X3 Currently these flags are not used.

# 3.5 Input/Output

Xl

The input and output buffers are treated as data memory locations. They are accessed using the ordinary memory reference instructions. The machine currently has a 4Kx16 data memory which requires 12 address lines (2<sup>12</sup>=4096). Since the data word is 16 bits, the 4 MSB's (bits 12-15) are available for other purposes. Setting bit 15 of the address to ONE causes data from the input buffer rather than the data memory to be placed on the bus. If the buffer has been already loaded by the external source (the host computer) and the flag is set to indicate the data is valid, the data is transferred immediately. On the other hand, if the flag has not yet been set, the computer will wait until valid data is

available. For Klatt's program this is not a limitation; the machine cannot proceed without having the latest phoneme in memory. The fact that once input is requested the machine must wait eliminates the need for an interrupt system with its complexity of hardware and software.

Examples of inputting data:

- 2. LOAD INDIRECT 11, INPUT (E)=((INPUT))→(Reg.11)

INPUT: 1000 0000 0000 0000

It is possible to test the input flag with the FLAG instruction and continue processing other data until the input data is valid.

N: FLAG 0 INPUT,50 Jump to N+50 if INPUT

flag is set to ONE. ELSE

continue processing

N+50: LOAD INDIRECT 11, INPUT Load data from input buffer into Reg. 11.

Output is handled in a similar fashion. Data can be transferred to the output buffer with either the STORE, STX, or OUTPUT instructions. Once again the buffer is treated as a data memory location. Bit 14 of

the effective address must equal ONE for the output to be the destintion rather than the data memory. The flag is tested before the buffer can be loaded; the machine waits until the flag is reset indicating the buffer is free.

Examples of outputting data:

- 2. STORE INDIRECT 11, OUT (Reg.11) → (E) = ((OUT))

OUT: 0100 0000 0000 0000

- 3. OUTPUT 12, START If Reg. 12 contains the number N, N adjacent memory locations starting at location START are transferred to the output buffer.

The machine checks that the data has been recieved by the external device before transferring more data.

The FLAG instruction can be used to test the output flag and continue processing other data until the output buffer is free to accept more data.

### CHAPTER 4

## Computer Architecture

Computer architecture refers to the organization and interconnection of the components of a computer system. Some of the basic building blocks include memories, registers, Arithmetic Logic Units (ALU's), multiplexers, and buses. These blocks can be configured in a wide variety of ways to implement a given task. Certain design constraints such as cost or speed help the computer architect choose the best way to select, connect, and control the various modules to perform their functions most efficiently. Very often there is a direct tradeoff between performance and price, so to minimize cost the machine should be designed to just meet the given design specifications. These constraints force the computer architect to be creative in his design.

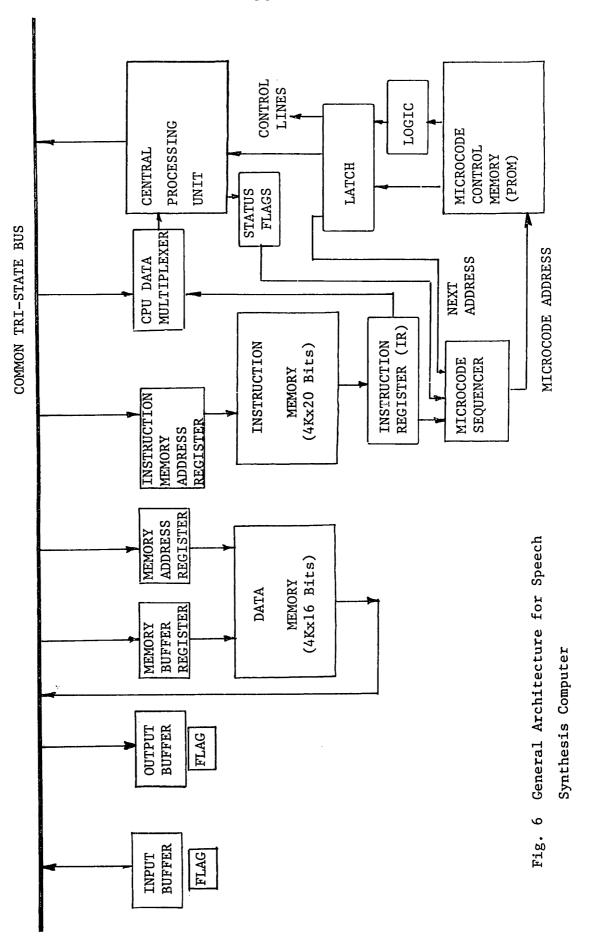

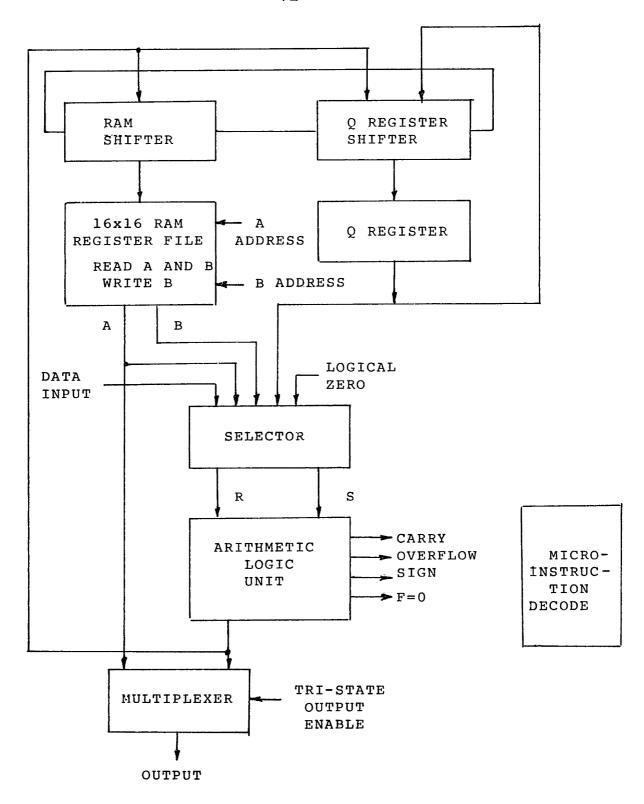

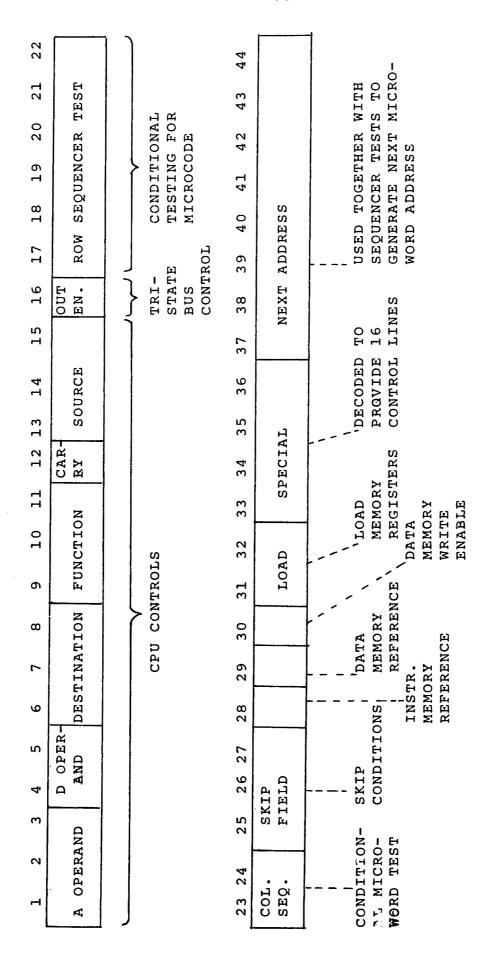

The overall architecture for the speech synthesis processor is shown in Fig. 6. Only after designing and reviewing dozens of alternatives was this particular structure chosen for its modularity, simplicity, speed, low cost, and flexibility.

## 4.1 Bus Organization

The processor uses a single bi-directional data/ address bus which is shared by the input buffer, output buffer, data memory, instruction memory, and the CPU. The bus contains 20 wires (wide enough for the 16 bit data words as well as the 20 bit instruction words), so information is transferred in parallel. Many machines have two or more buses and all data must first pass through the CPU, however the single bus arrangement allows direct communication among all devices. example, data can be transferred from the data memory to the output buffer while the CPU is busy performing an entirely different operation. This bus structure is extremely modular and easily expandable. The processor as a research tool will almost certainly undergo changes, and other memories, processors, and peripherals can be attached directly to the main bus with only minor hardware alterations.

In a single bus system, during a given cycle, only one device can transmit data while one or more devices can receive data. A problem that frequently arises in a single bus system is one of arbitration, that is, two devices may request to transmit data on the bus at the same time. In this machine, only the input buffer, data memory, and CPU can supply data to the bus. The micro-

program control has been designed in such a way that there is never a conflict; the machine never wastes a cycle while a device requests the use of the bus. The use of single bus combined with tri-state logic (the three stable states are 0, 1, and a high impedance disabled state) maximizes the number of direct data paths while eliminating the need for all but one multiplexer.

The one multiplexer shown controlling the source of data for the CPU was included for the case when the displacement field must be obtained from the Instruction Register (IR), altered by the CPU, and transmitted to the bus all in one machine cycle. If this multiplexer were omitted and the IR fed the instruction directly onto the bus an extra cycle would be required: during the first cycle the contents of the IR would be entered into the CPU via the bus, and during the second the CPU resultant address would be transmitted on the bus. This savings is significant since it is realized for every macroinstruction executed. The overall processor speed is increased by approximately 20% at the cost of only four additional integrated circuits.

# 4.2 Input/Output

All instructions and data are entered into the

machine via the input buffer which momentarily holds information being transferred into the computer. buffer is loaded asynchronously from either the front panel or an external source (i.e. another computer). A separate output buffer provides the interface to the vocal tract model. A single bit flag for each buffer is set when the buffer is busy and reset when it is Both buffers appear to the programmer as data memory locations and can be used in any memory reference instruction. The need for special I/O instructions is replaced by the ordinary LOAD and STORE instructions. When loading from input the processor checks the status flag and waits for valid data. Similarly, when storing data in the output buffer the machine waits until the buffer is ready to receive more data.

In machines where the external devices operate several orders of magnitude slower than the computer, it is desirable to incorporate interrupts so that the machine can continue processing as it waits for data. This is not a problem in the speech processor, so an interrupt system is not included. Interrupts require significant overhead since the state of the processor must be saved before handling the interrupt request and restored afterwards.

## 4.3 Data and Instruction Memories

The computer contains separate data and instruction memories. The data memory (4K X 16 bits) has a Memory Address Register (MAR) which is loaded with the address of the location to accessed, and a Memory Buffer Register (MBR) which contains any data to be written into the memory. These registers hold the address and data for the duration of a memory cycle which is almost three times slower than the CPU cycle time. Once they are loaded the bus is freed so the machine can continue processing concurrently with the memory reference.

The instruction memory is currently 4K X 20 bits.

Together with the data memory this is large enough to hold present and projected speech synthesis programs.

The instruction memory has its own address register, but no data buffer register. Referring back to Fig. 6, the output of the instruction memory goes directly to the IR without first passing through a memory buffer register.

Elimination of this buffer reduces the chip count without limiting the machine's power (since the particular memory chip used contains internal data buffers).

During program loading (a relatively infrequent operation) the instructions are passed directly from the Input Buffer to the instruction memory. This is the only time the instruction memory is written into: instructions

cannot be altered during normal program execution.

The basic storage device for both memories is a 4K X 1 bit static NMOS random access memory (RAM). The memories can easily be expanded in width or length by simply extending the buffer registers and using more memory chips. The length of the instruction word can also be increased by single bit increments, to increase the power of the instruction set. The memory length can be quadrupled with a 16K X 1 bit RAM that is pin-for-pin compatible with the 4K's and is expected to be introduced into the commercial market during the next year. To use these, the two extra leads that are not connected for the 4K RAM would become the two most significant address lines. The control signals for such a memory would remain unchanged.

It is important to realize that the data and instruction memories are not only separate but of different widths. The reasons for this somewhat unconventional arrangement are:

1. Separate memories allow for concurrent reading and/or writing of data and instructions. Although a high speed memory (215 nanosecond access, 400 ns cycle time) is used, the CPU cycle time is only 150 ns. Since the memory is the slowest part of the system, it is desir-

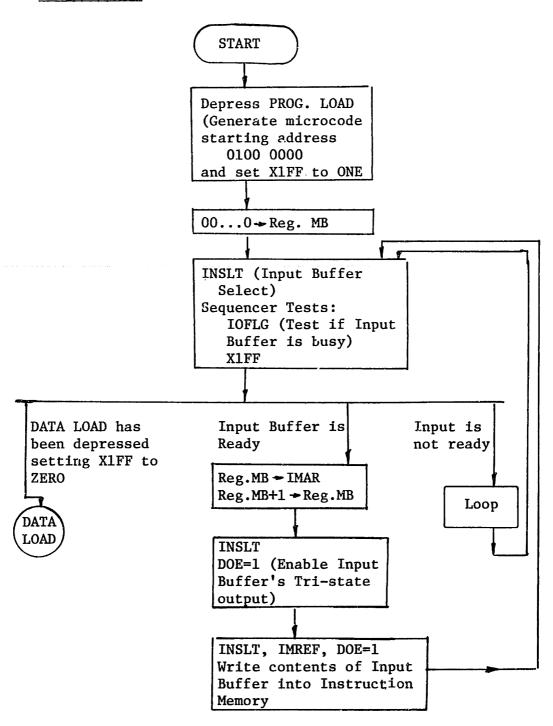

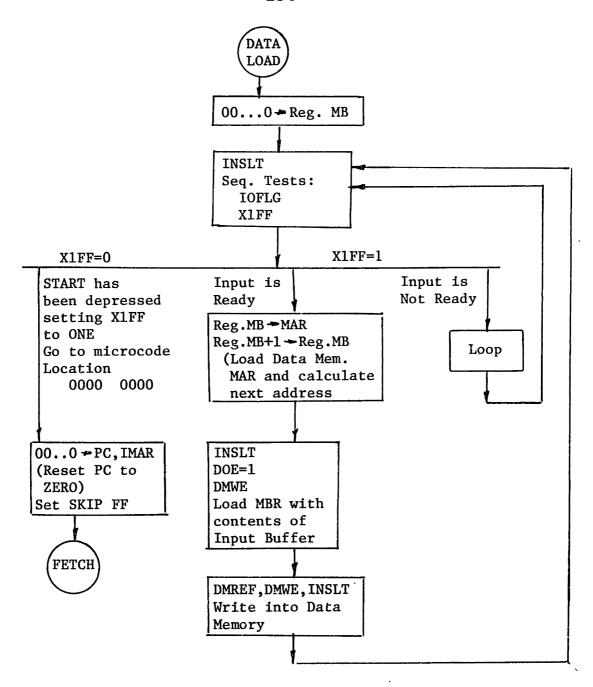

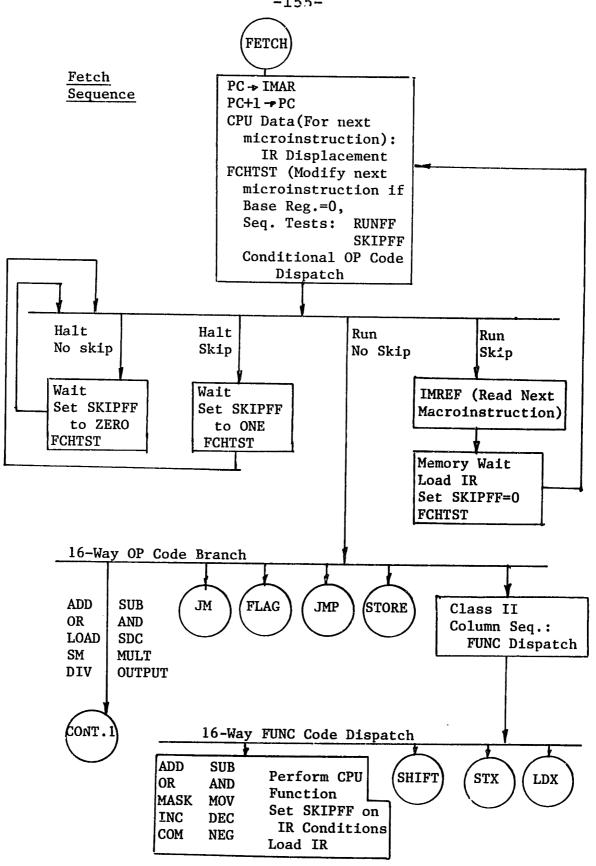

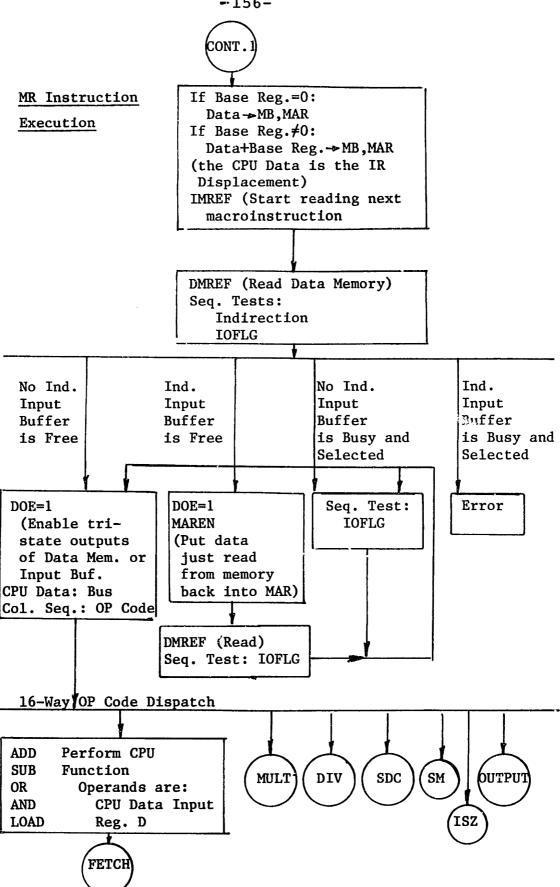

able to be able to read or write in the data memory while reading the next instruction from the instruction memory. Performing these functions together can save up to 400 ns from the macroinstruction cycle, depending on the particular instruction.