# Cache Coherence Protocols for Large-Scale Multiprocessors

by

#### David Lars Chaiken

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### September 1990

© Massachusetts Institute of Technology, 1990

The author hereby grants to MIT permission to reproduce and to distribute copies of this thesis document in whole or in part.

| gnature of Author                                                  |

|--------------------------------------------------------------------|

| Department of Electrical Engineering and Computer Science          |

| August 31, 1990                                                    |

| ertified by                                                        |

| Anant Agarwal                                                      |

| Assistant Professor of Computer Science and Electrical Engineering |

| Thesis Supervisor                                                  |

| ccepted by                                                         |

| Arthur C. Smith                                                    |

| Chairman, Departmental Committee on Graduate Students              |

#### Cache Coherence Protocols for Large-Scale Multiprocessors

by

#### David Lars Chaiken

Submitted to the Department of Electrical Engineering and Computer Science on August 31, 1990, in partial fulfillment of the requirements for the degree of

Master of Science

#### Abstract

Caches have the potential to provide multiprocessors with an automatic mechanism for reducing both network traffic and average memory access latency. However, cachebased systems must address the problem of cache coherence. This thesis presents the results of the search for a cache coherence solution for Alewife, a large-scale multiprocessor being built at MIT. The research focuses on coherence protocols that use a directory, a list of cached copies of data, to avoid the need for a system-wide broadcast mechanism. The structure and the implementation of a number of coherence schemes are evaluated with coupled and decoupled simulation techniques. In addition to comparing the protocols in terms of hardware overhead and performance, the thesis reports on the experience gained by implementing several different schemes in ASIM, the Alewife machine simulator. The protocol search reaches two major conclusions: First, by using system-level optimizations, it is possible to use caches to build large-scale shared-memory multiprocessors. Second, the Alewife machine should use the integrated systems approach — handling common cases in hardware and exceptional cases in software — to solve the cache coherence problem.

**Keywords:** cache coherence, multiprocessor system, directory, multiprocessor simulation, shared-memory multiprocessor, interconnection network

Thesis Supervisor: Anant Agarwal

Title: Assistant Professor of Computer Science and Electrical Engineering

#### Acknowledgments

I could not have completed this thesis without help from many people. It was during the spring before I entered MIT that Anant Agarwal, my thesis advisor, gave me an introductory tutorial on cache-coherent multiprocessors. At that time, I had no idea that the topic was going to occupy me for the following two years. Since then, Professor Agarwal has taught me how to reason about computer architectures, how to evaluate alternatives for designing multiprocessors, and how to communicate my ideas to other researchers. It has been a pleasure to be a member of Anant's research group.

Most of the ideas that this thesis evaluates were developed through a joint effort of the Alewife group at MIT. The other members of the group have been my teachers, conspirators, and friends. By advising me when I arrived at MIT, Gino Maa gave me the assistance that I needed to start doing the research that led to my thesis. Gino also wrote the network simulator that I used to analyze the cache coherence schemes. Not only did Beng-Hong Lim manage to tolerate sharing an office with me for two years (so far), but he also wrote portions of the SPARCLE processor simulator and run-time system. Mathews Cherian laid the foundation for my work by writing both the post-mortem scheduler with Kimming So at IBM and the cache and directory simulator. Kiyoshi Kurihara wrote the dynamic post-mortem scheduler and worked with me to understand the balance between software and hardware in shared-memory multiprocessors. By questioning and challenging my ideas, no matter how great or how small, Dan Nussbaum has increased my knowledge in many areas of computer science. David Kranz wrote the Mul-T compiler, which is the foundation of Alewife's software system. My discussions with David have given me a practical understanding of the power and the limitations of compilers and run-time systems. Kirk Johnson has helped me gain insight into the difficult job of programming parallel processing systems. Kirk was responsible for the results derived from the Speech application, which he wrote. John Kubiatowicz, who has led the hardware design effort for Alewife, worked with me to develop an accurate model of the cache controller. I have enjoyed

long design sessions with Kubi, which typically resulted in frustration, understanding, and (I hope) an efficient design for Alewife's memory system implementation. I look forward to continuing to work as a member of the Alewife team.

The evaluation methodology used in this thesis required support from a wide range of sources outside of MIT. Harold Stone and Kimming So of IBM helped obtain the traces of the Weather, Simple, and FFT programs. Pat Teller and Allan Gottlieb of New York University arranged to send me the sources for these programs. Wolf-Dietrich Weber and Anoop Gupta provided the four VAX T-bit traces, which were generated using a system developed by Steve Goldschmidt at Stanford. The notation for the protocol state transition diagrams borrows from the doctoral thesis of James Archibald and from work done in the MIT Parallel Processing Group by Ingmar Vuong-Adlerberg. Digital Computer Corporation, Encore Computer Corporation, Harris Computer Systems, and SUN Microsystems contributed the machines that I have used to analyze the performance of large-scale multiprocessors. The research reported in this thesis is funded by DARPA contract # N00014-87-K-0825.

I would also like to thank Ema and Aba for encouraging and supporting my education. And finally, hugs to Ora for reminding me that there are many things that are more important than coherent caches.

Praised are You, the Eternal, our God, Ruler of the Universe, who has graced us with life, sustained us, and allowed us to reach this season.

# Contents

| 1 | Intr | roduction                                           | 13        |

|---|------|-----------------------------------------------------|-----------|

|   | 1.1  | Cache Coherence for the Alewife Machine             | 14        |

|   | 1.2  | Cache Coherence as a General Problem                | 15        |

|   | 1.3  | Organization of this Thesis                         | 17        |

| 2 | Bac  | ekground                                            | 18        |

|   | 2.1  | Why Study Caches?                                   | 18        |

|   |      | 2.1.1 Single Processor Caches                       | 18        |

|   |      | 2.1.2 Multiprocessor Caches                         | 20        |

|   | 2.2  | The Cache Coherence Problem                         | 2.        |

|   |      | 2.2.1 Classes of Cache Coherence Protocols          | 23        |

|   | 2.3  | Directory-Based Cache Coherence Protocols           | $2^{\xi}$ |

|   | 2.4  | Qualitative Evaluation of the Protocols             | 3.        |

| 3 | Imp  | plementing Cache Coherence in Alewife               | 33        |

|   | 3.1  | Scalability and Programmability                     | 33        |

|   |      | 3.1.1 The Alewife Processing Node                   | 34        |

|   |      | 3.1.2 Latency Avoidance                             | 36        |

|   |      | 3.1.3 Latency Tolerance                             | 3         |

|   | 3.2  | Implementing Directory Protocols                    | 3         |

|   |      | 3.2.1 The LimitLESS Directory Protocol              | 39        |

|   |      | 3.2.2 A Simple Model of the LimitLESS Protocol      | 40        |

|   |      | 3 2 3 Background: Implementing a Full-Map Directory | 4         |

|   |     | 3.2.4  | Specification of the LimitLESS Scheme         | 4  |

|---|-----|--------|-----------------------------------------------|----|

|   |     | 3.2.5  | Estimating LimitLESS Directory Performance    | 48 |

|   | 3.3 | Imple  | mentation Issues in Alewife                   | 49 |

|   |     | 3.3.1  | Alewife's Processor-Controller Interface      | 49 |

|   |     | 3.3.2  | Support for Multiple Contexts                 | 50 |

|   | 3.4 | Secon  | d-Order Considerations                        | 64 |

|   |     | 3.4.1  | Protocol Messages                             | 64 |

|   |     | 3.4.2  | Counting Acknowledgments                      | 68 |

|   |     | 3.4.3  | Evaluation of Secondary Protocol Features     | 69 |

| 4 | Eva | luatio | n Methodology                                 | 71 |

|   | 4.1 | Overv  | iew                                           | 7. |

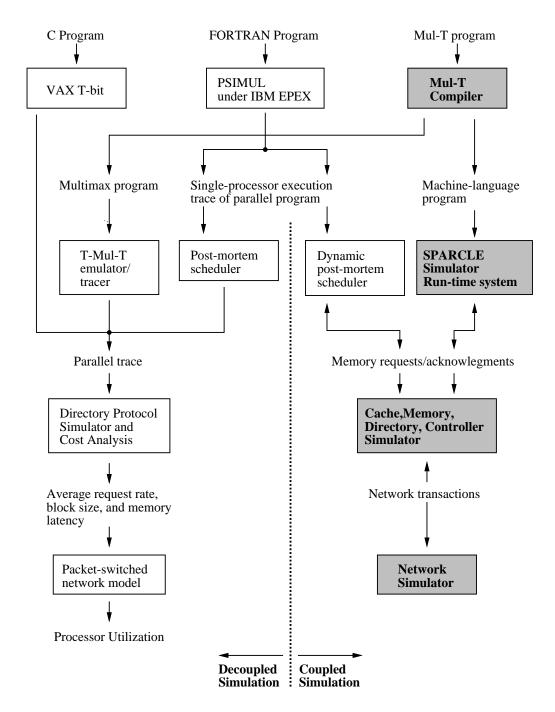

|   | 4.2 | Decou  | pled Simulation                               | 74 |

|   |     | 4.2.1  | Getting Multiprocessor Address Trace Data     | 75 |

|   |     | 4.2.2  | Simulating a Cache Coherence Strategy         | 7  |

|   |     | 4.2.3  | The Interconnection Network Model             | 79 |

|   |     | 4.2.4  | A Sample Computation of Processor Utilization | 8. |

|   |     | 4.2.5  | Sources of Error in Decoupled Simulations     | 82 |

|   | 4.3 | Coupl  | ed Simulation                                 | 83 |

|   |     | 4.3.1  | Alewife System Simulator                      | 83 |

|   |     | 4.3.2  | Dynamic Post-Mortem Scheduling                | 86 |

|   |     | 4.3.3  | Sources of Error in Coupled Simulations       | 8  |

|   | 4.4 | Valida | ating Decoupled Simulation                    | 88 |

|   |     | 4.4.1  | Parameter Adjustment                          | 90 |

|   |     | 4.4.2  | The Effect of Hot-Spot Contention             | 9. |

|   |     | 4.4.3  | The Processor Utilization Metric              | 9! |

| 5 | Ana | alysis |                                               | 97 |

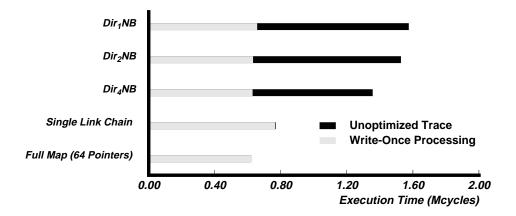

|   | 5.1 | Perfor | rmance of Cache Coherence Schemes             | 98 |

|   |     | 5.1.1  | Analysis of Directory Schemes                 | 98 |

|   |     | 5 1 2  | Are Caches Useful for Shared Data?            | 98 |

|   |     | 5.1.3 Limited Directory Performance                     | 101 |

|---|-----|---------------------------------------------------------|-----|

|   |     | 5.1.4 Chained Directory Performance                     | 101 |

|   | 5.2 | Improving the Performance of Directories                | 103 |

|   |     | 5.2.1 Optimizing Synchronization Variables              | 103 |

|   |     | 5.2.2 Optimizing Read-Only Data                         | 104 |

|   |     | 5.2.3 Optimizing Write-Once Data                        | 106 |

|   |     | 5.2.4 Implications of Directory Optimization Techniques | 107 |

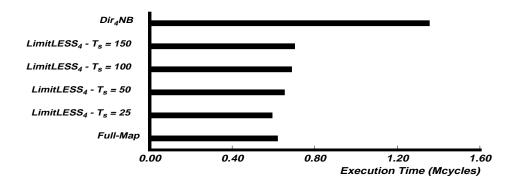

|   | 5.3 | LimitLESS Directory Protocol Performance                | 108 |

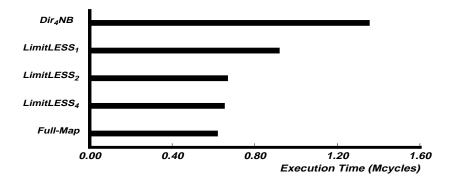

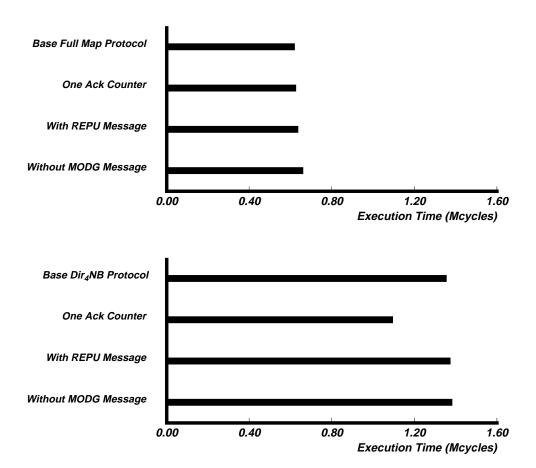

|   | 5.4 | Implementation Issues                                   | 110 |

|   |     | 5.4.1 Weak Ordering versus Multiple Contexts            | 110 |

|   |     | 5.4.2 Second-Order Effects                              | 113 |

|   | 5.5 | Conclusions                                             | 116 |

| A | Tab | les of Statistics                                       | 118 |

|   | A.1 | Trace-Driven Simulation Results                         | 118 |

|   | A.2 | Dynamic Post-Mortem Scheduler                           | 122 |

| В | Cac | he Coherence Protocol Specification for ASIM            | 124 |

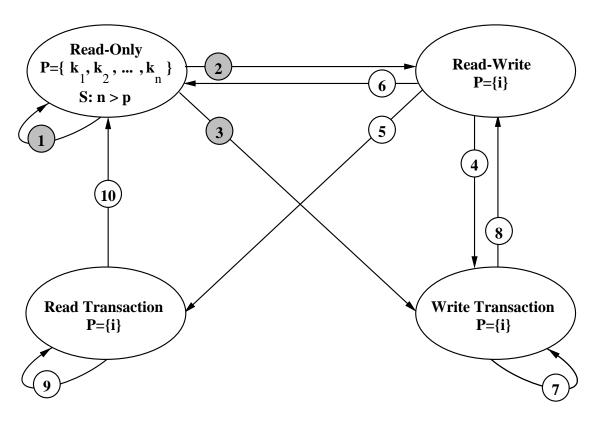

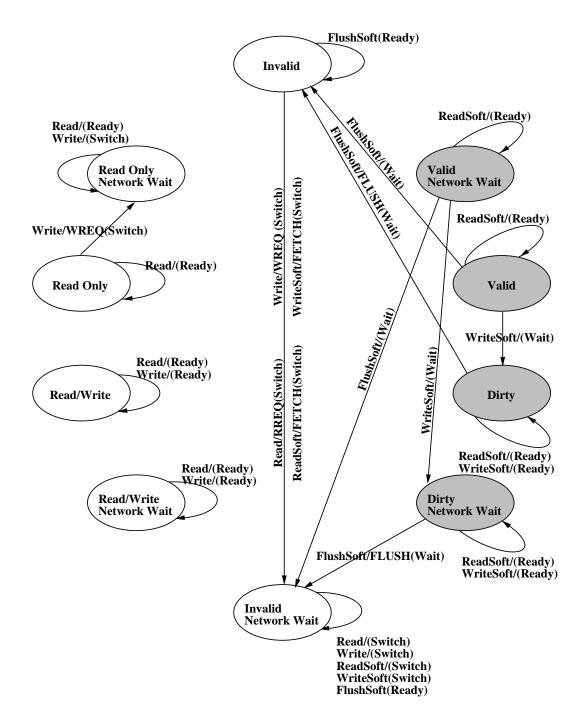

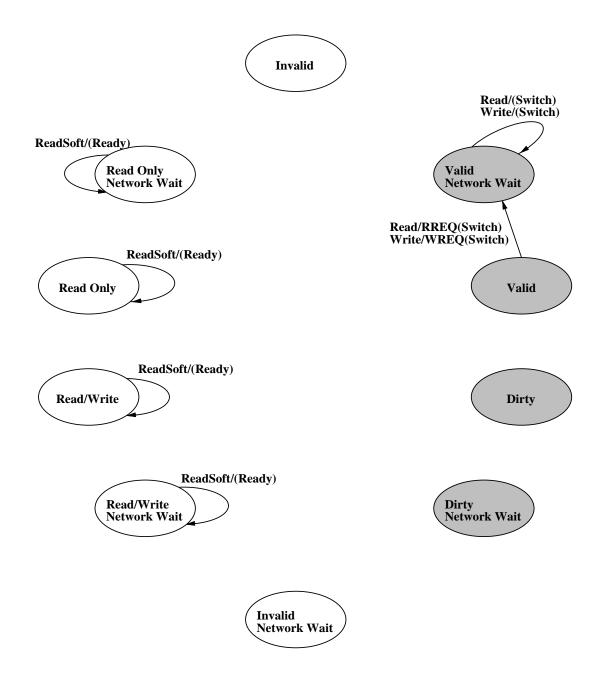

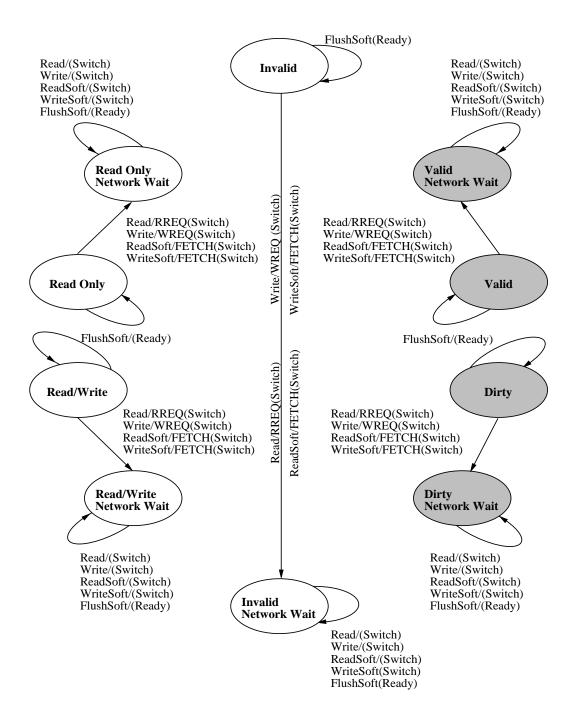

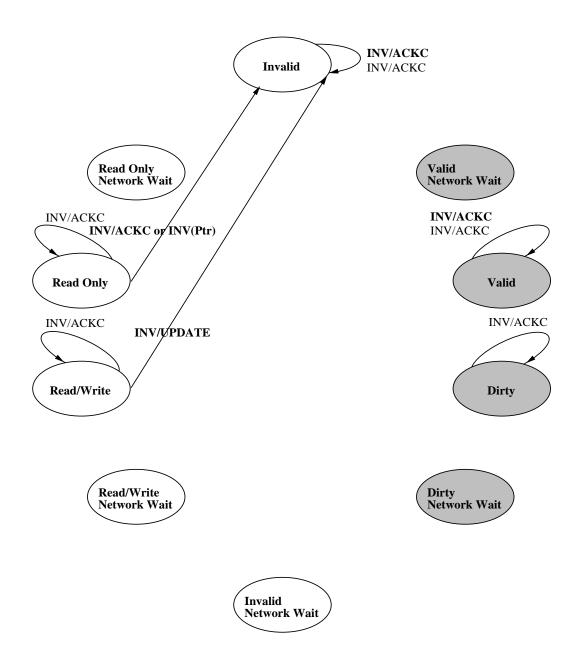

|   | B.1 | The State Transition Diagrams                           | 124 |

|   | B.2 | Hardware Coherence Protocols                            | 145 |

|   |     | B.2.1 Protocol States                                   | 145 |

|   |     | B.2.2 Protocol Messages                                 | 147 |

|   | B.3 | Software Coherence Protocol                             | 147 |

|   | D 4 | Interaction between Hardware and Software Coherence     | 148 |

# List of Figures

| 1-1 | The implementation of a shared-memory model must be divided be-           |    |

|-----|---------------------------------------------------------------------------|----|

|     | tween the processor and the memory system                                 | 16 |

| 2-1 | Illustration of the cache coherence problem                               | 21 |

| 2-2 | Three types of directory protocols                                        | 27 |

| 3-1 | An Alewife processing element with a LimitLESS directory entry            | 35 |

| 3-2 | Full-map and limited directory entries. The full-map pointer array is     |    |

|     | optimized as a bit-vector. The limited directory entry has four pointers. | 42 |

| 3-3 | Directory state transition diagram for the full-map and LimitLESS         |    |

|     | coherence schemes                                                         | 45 |

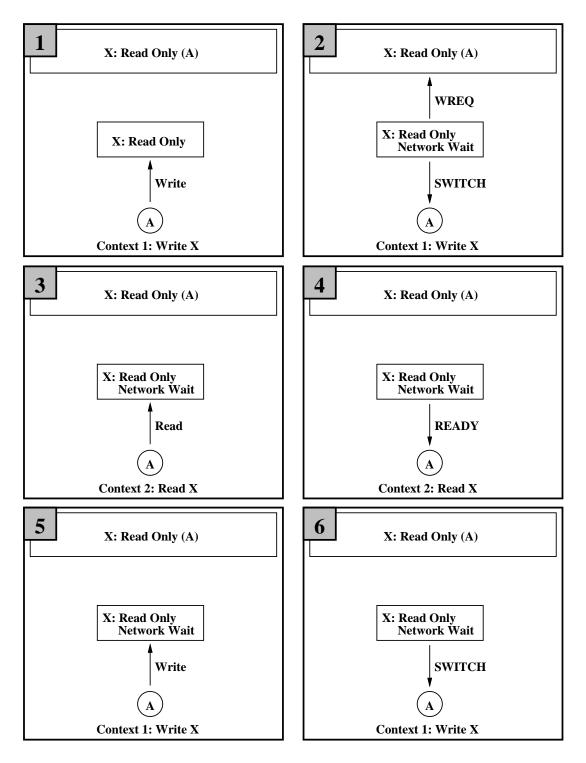

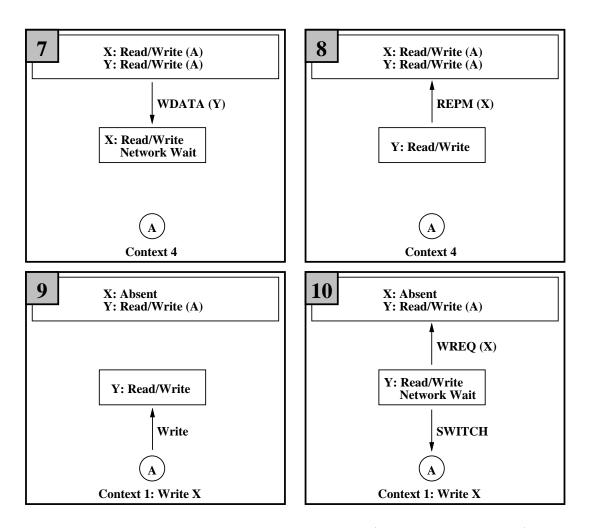

| 3-4 | Scenario involving a network wait state. (Frames 1 through 6.)            | 53 |

| 3-5 | Scenario involving a network wait state. (Frames 7 through 10.)           | 54 |

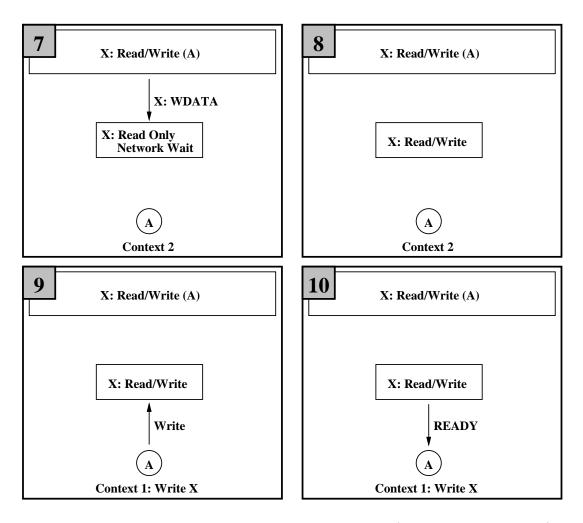

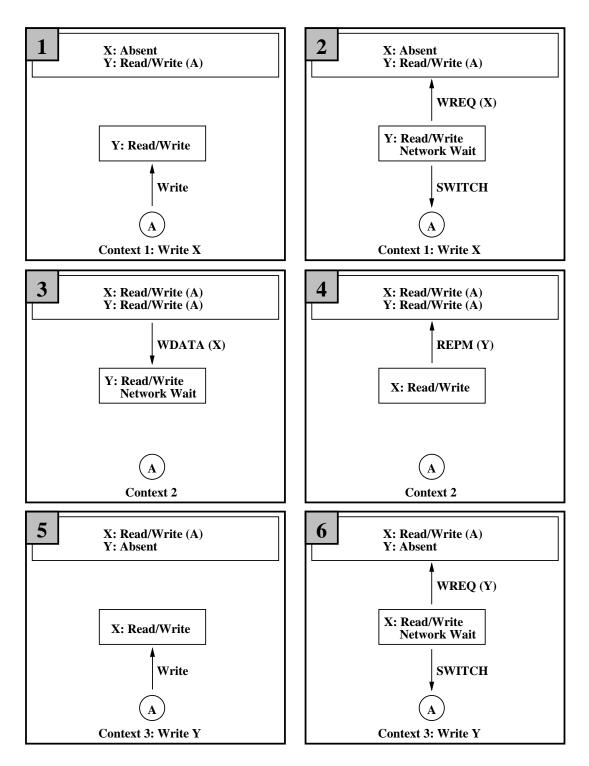

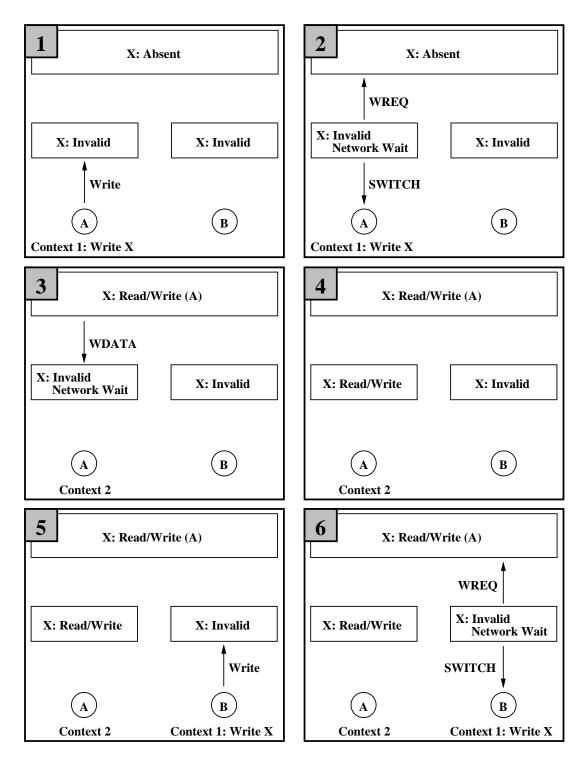

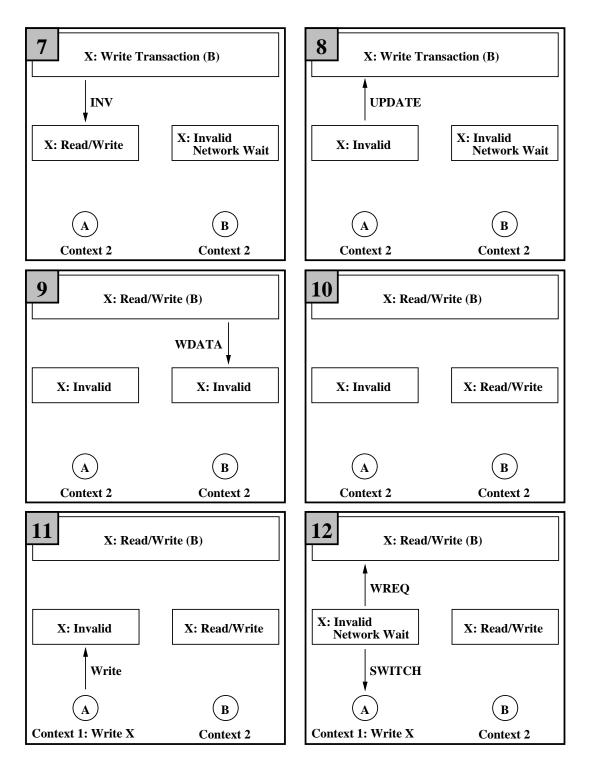

| 3-6 | Replacement thrashing scenario. (Frames 1 through 6.)                     | 56 |

| 3-7 | Replacement thrashing scenario. (Frames 7 through 10.)                    | 57 |

| 3-8 | Invalidation thrashing scenario. (Frames 1 through 6.)                    | 58 |

| 3-9 | Invalidation thrashing scenario. (Frames 7 through 12.)                   | 59 |

| 4-1 | Simulation environments used to evaluate the performance of cache         |    |

|     | coherence protocols. The shaded rectangles represent ASIM                 | 72 |

| 4-2 | Comparison of processor utilization measurements for the Weather ap-      |    |

|     | plication, obtained from coupled and decoupled evaluation methodolo-      |    |

|     | gies                                                                      | 89 |

| 4-3 | Comparison of processor utilization measurements for Weather, before    |      |

|-----|-------------------------------------------------------------------------|------|

|     | adjusting the base memory access latency.                               | 90   |

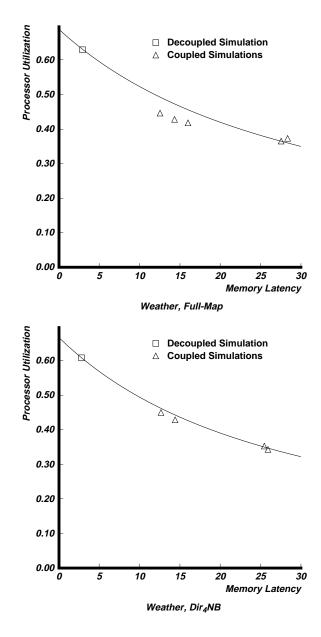

| 4-4 | Processor utilization versus memory latency. The curve indicates the    |      |

|     | prediction of the network model. The individual points are data from    |      |

|     | simulations                                                             | 92   |

| 4-5 | Comparison of processor utilization measurements for Weather, after     |      |

|     | adjusting the memory latency, but before eliminating the hot-spot       | 93   |

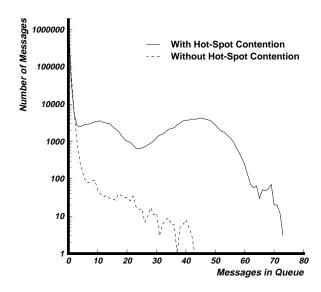

| 4-6 | Cache controller queue sizes with $Dir_4NB$ protocol                    | 94   |

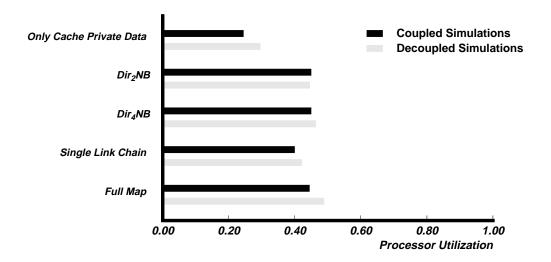

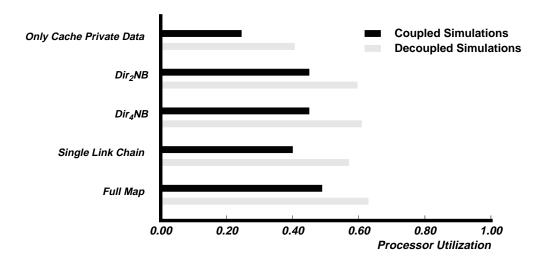

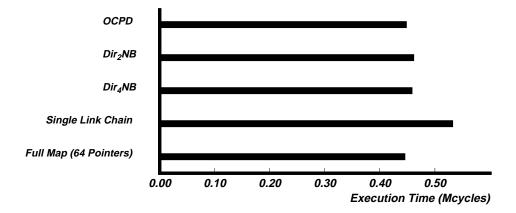

| 4-7 | Comparison of coherence schemes using coupled simulations               | 95   |

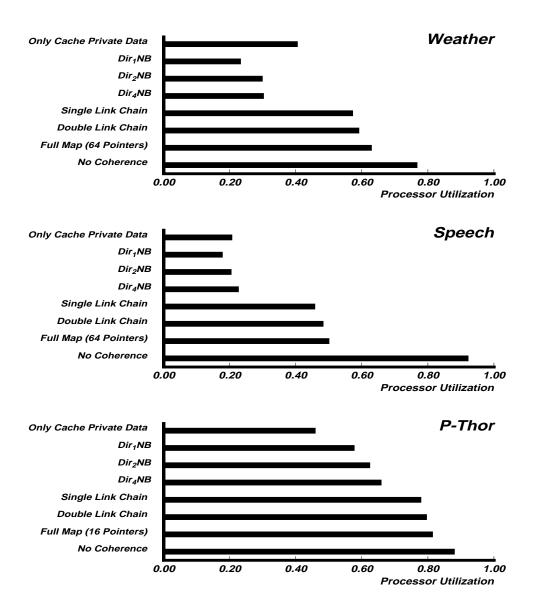

| 5-1 | Comparison of coherence schemes                                         | 100  |

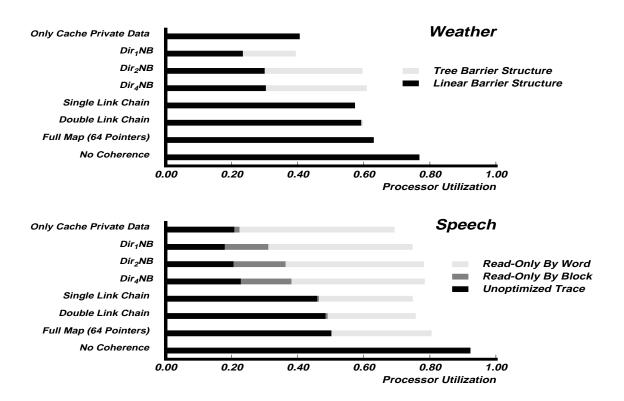

| 5-2 | System-level optimizations                                              | 105  |

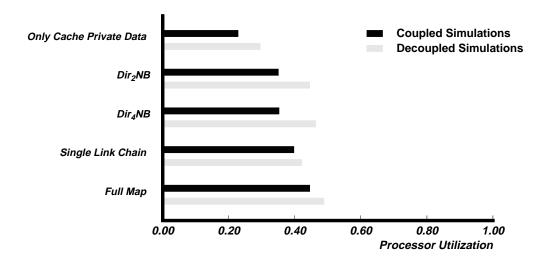

| 5-3 | Comparison of coherence schemes after write-once optimization           | 107  |

| 5-4 | Weather, 64 Processors, LimitLESS with 25 to 150 cycle directory        |      |

|     | emulation latencies                                                     | 109  |

| 5-5 | Weather, 64 Processors, LimitLESS scheme with 1, 2, and 4 hardware      |      |

|     | pointers                                                                | 109  |

| 5-6 | The effect of protocol implementation on the performance of Weather.    | 115  |

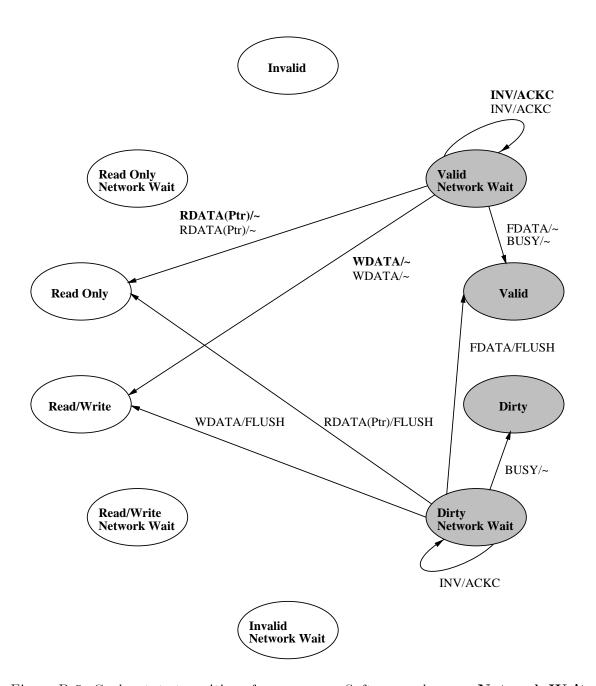

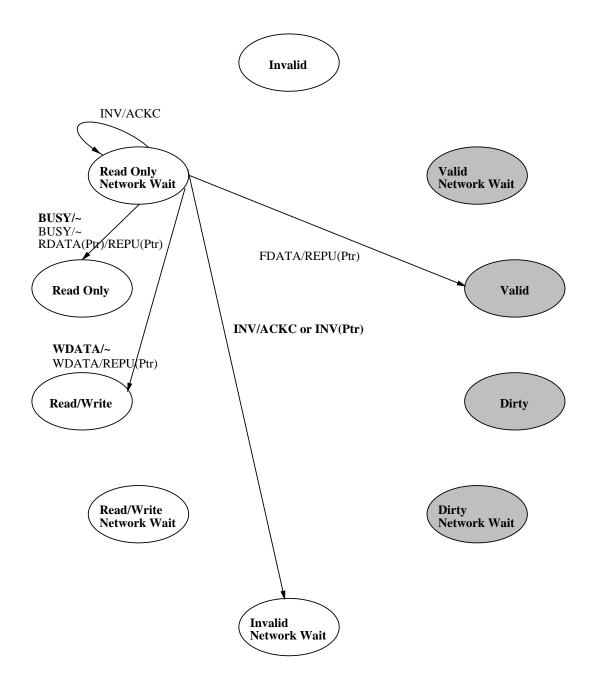

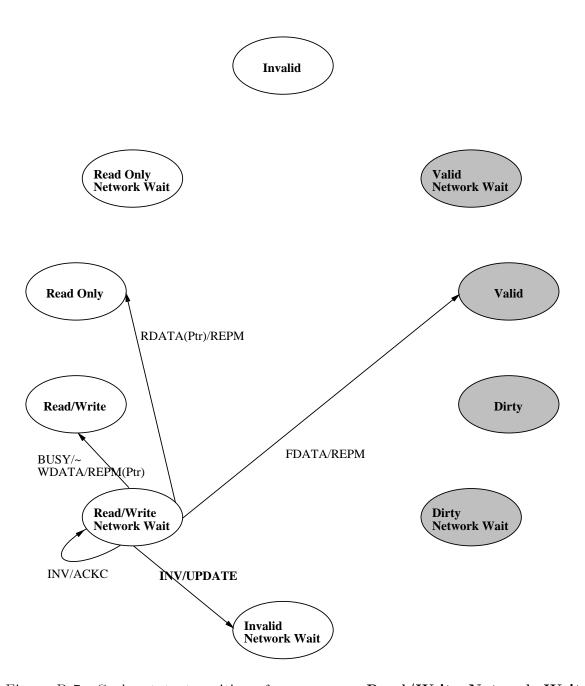

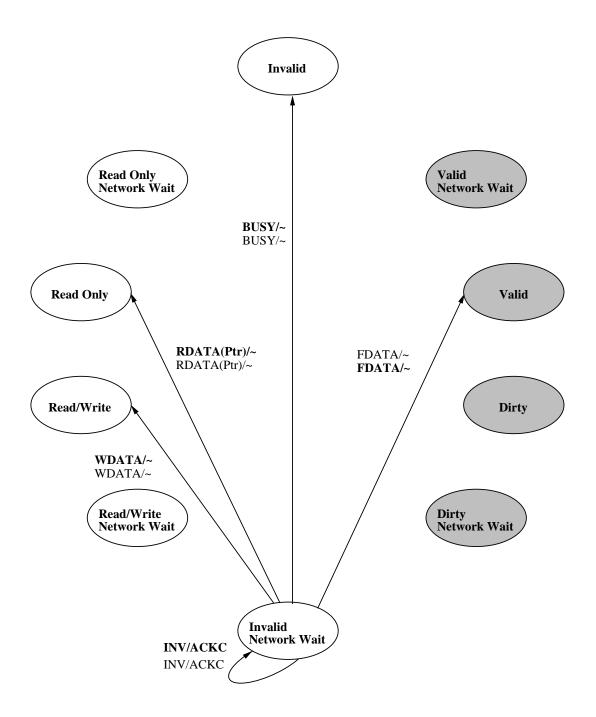

| B-1 | Cache state transitions for processor requests when the tag matches     | 127  |

| B-2 | Cache state transitions for processor requests when the tag matches,    |      |

|     | hardware/software coherence interaction                                 | 128  |

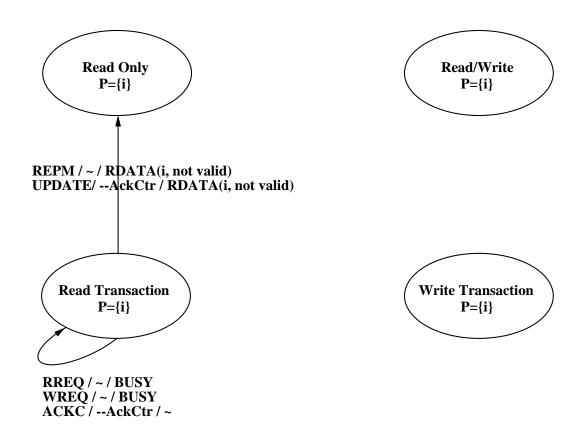

| B-3 | Cache state transitions for processor requests when the tag does not    |      |

|     | match                                                                   | 129  |

| B-4 | Cache state transitions for messages: Non-network-wait states           | 130  |

| B-5 | Cache state transitions for messages: Software coherence <b>Network</b> |      |

|     | Wait states                                                             | 131  |

| B-6 | Cache state transitions for messages: Read Only Network Wait state      | .132 |

| B-7 | Cache state transitions for messages: Read/Write Network Wait           |      |

|     | state                                                                   | 133  |

| B-8 | Cache state transitions for messages: Invalid Network Wait state.       | 134  |

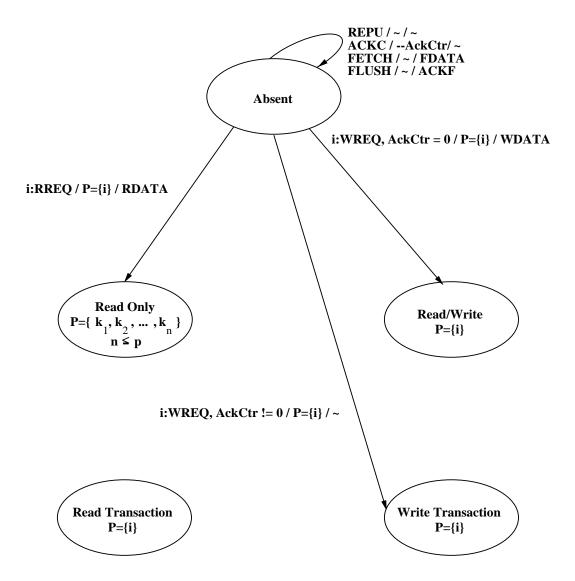

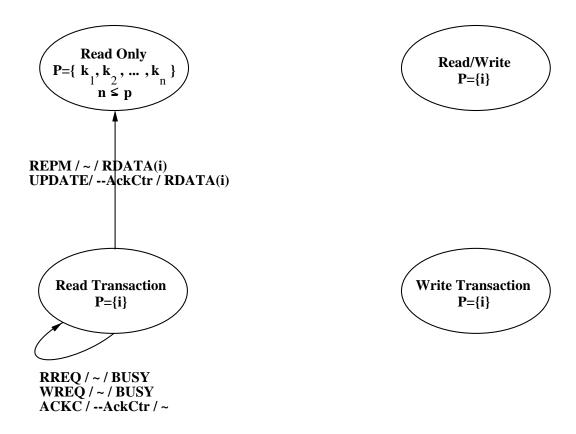

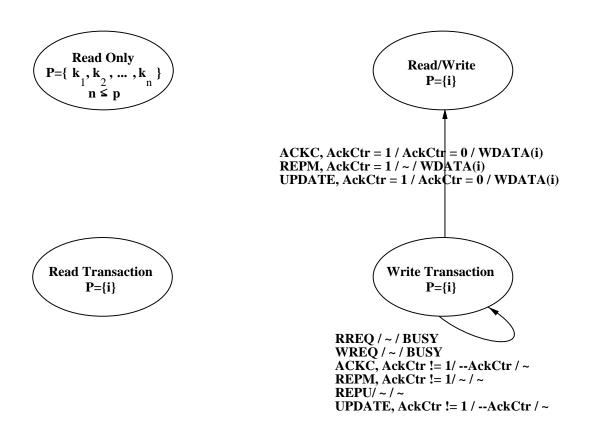

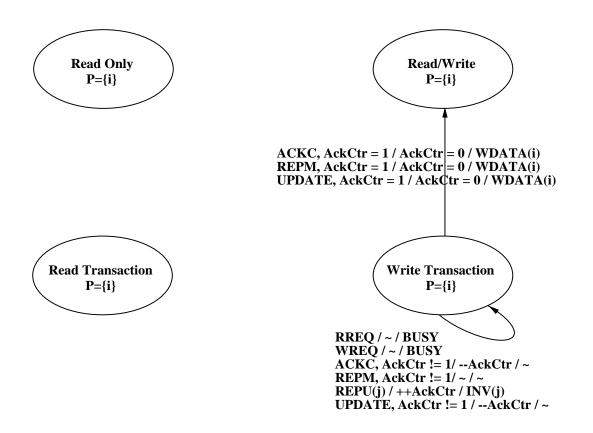

| B-9  | Memory state transitions for limited directory: <b>Absent</b> state         | 135 |

|------|-----------------------------------------------------------------------------|-----|

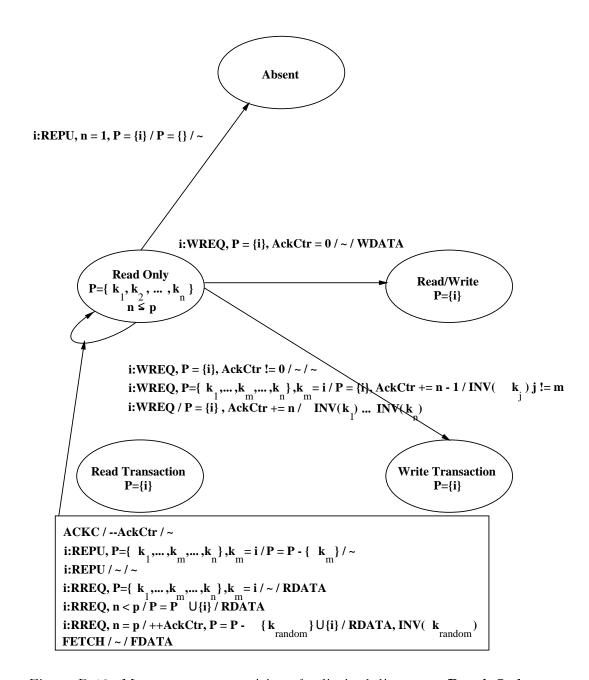

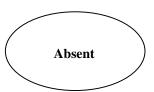

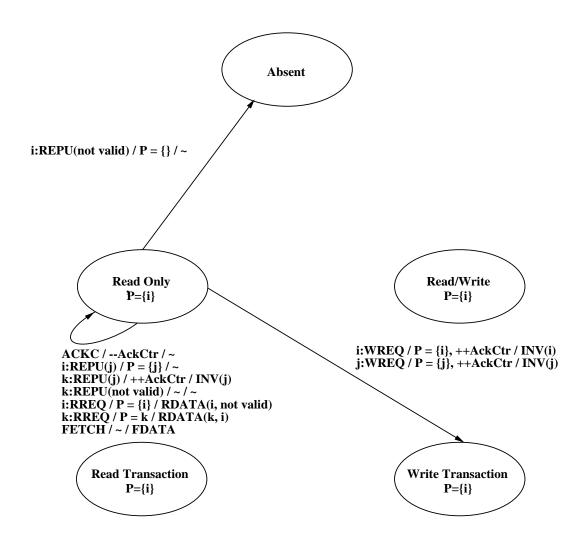

| B-10 | Memory state transitions for limited directory: Read Only state             | 136 |

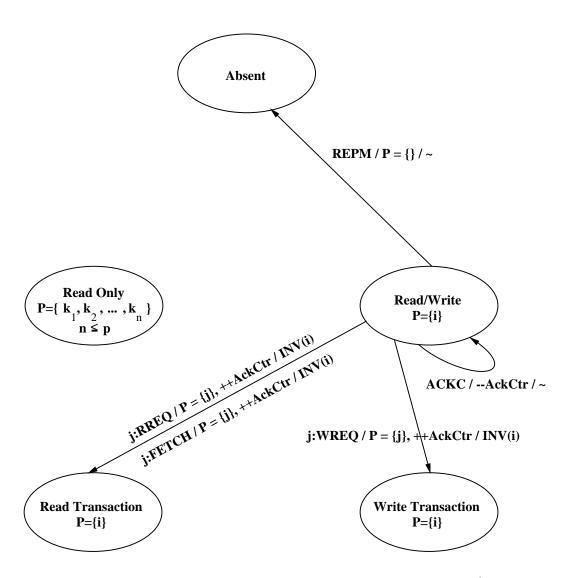

| B-11 | Memory state transitions for limited directory: $\mathbf{Read/Write}$ state | 137 |

| B-12 | Memory state transitions for limited directory: Read Transaction            |     |

|      | state                                                                       | 138 |

| B-13 | Memory state transitions for limited directory: Write Transaction           |     |

|      | state                                                                       | 139 |

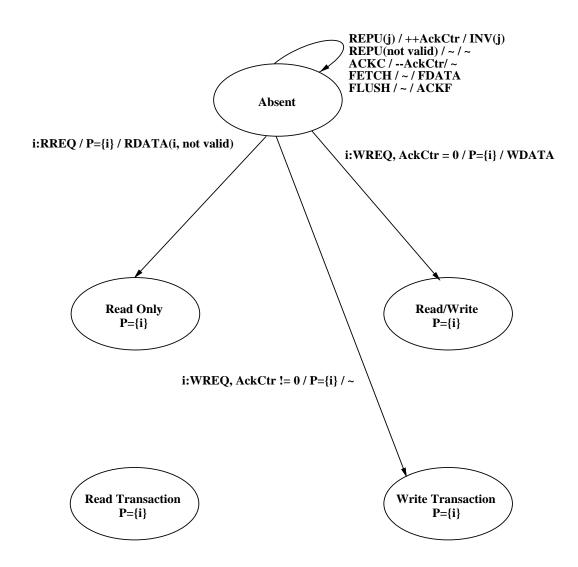

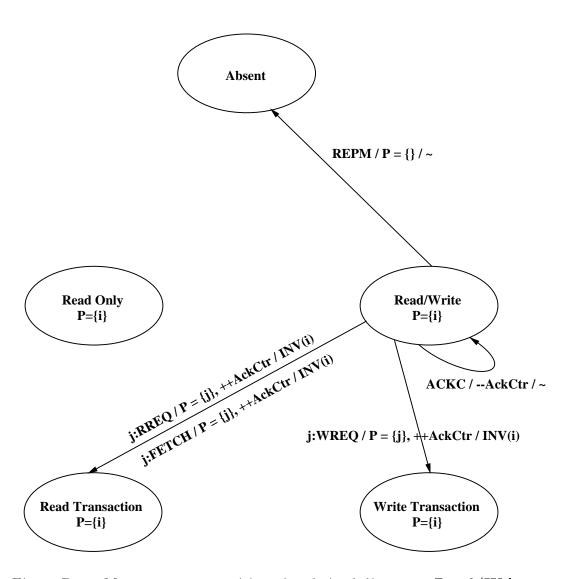

| B-14 | Memory state transitions for chained directory: Absent state                | 140 |

| B-15 | Memory state transitions for chained directory: Read Only state             | 141 |

| B-16 | Memory state transitions for chained directory: Read/Write state            | 142 |

| B-17 | Memory state transitions for chained directory: Read Transaction            |     |

|      | state                                                                       | 143 |

| B-18 | Memory state transitions for chained directory: Write Transaction           |     |

|      | state                                                                       | 144 |

# List of Tables

| 3.1 | Directory states                                                         | 42  |

|-----|--------------------------------------------------------------------------|-----|

| 3.2 | Annotation of the state transition diagram                               | 46  |

| 3.3 | Cache coherence protocol messages                                        | 47  |

| 3.4 | Controller Response Types                                                | 50  |

| 3.5 | Cache network wait states                                                | 52  |

| 3.6 | Optional protocol messages                                               | 65  |

| 4.1 | Summary of Trace Statistics: Length values are in millions of references |     |

|     | to memory                                                                | 75  |

| 4.2 | Transaction Types and Costs                                              | 79  |

| 4.3 | Simulation parameter defaults for the cache, directory, and network      | 80  |

| 4.4 | Simulation parameter defaults for ASIM                                   | 84  |

| 5.1 | Average latency statistics (in processor cycles) for the Weather appli-  |     |

|     | cation with combining tree synchronization and write-once data opti-     |     |

|     | mization                                                                 | 103 |

| 5.2 | Comparison of Lower Bound on Weak Ordering and Exact Simulation          |     |

|     | of Multiple Contexts. Units are in Processor Execution Cycles            | 113 |

| A.1 | Simulation results for FORTRAN application suite                         | 119 |

| A.2 | Simulation results for the C and Mul-T application suites                | 120 |

| A.3 | Results for Weather with combining tree synchronization                  | 121 |

| A.4 | Results for Speech with read-only data processing                        | 121 |

| A.5 | Results for Weather with combining tree synchronization                  | 122 |

| A.6 | Results for Simple with combining tree synchronization | 123 |

|-----|--------------------------------------------------------|-----|

| В.1 | Processor Request Types                                | 125 |

| B.2 | Controller Response Types                              | 125 |

| В.3 | Correspondence between Transition Diagrams and Figures | 125 |

| B.4 | Cache states for hardware coherence                    | 146 |

| B.5 | Directory states for hardware coherence                | 146 |

| B.6 | Protocol messages for hardware coherence               | 147 |

| B.7 | Cache states for software coherence                    | 147 |

| В 8 | Protocol messages for software coherence               | 148 |

# Chapter 1

### Introduction

A multiprocessor's shared-memory system provides a mechanism for programmers to partition programs among many processors, and allows the processors to communicate and to synchronize with each other. As processing speed increases relative to the latency of interprocessor communication, the latency and the bandwidth of the memory system limits the speed of computation. Small multiprocessors remove this mismatch between processor and memory speeds by equipping each processor with a fast, local memory, called a cache. By storing copies of frequently accessed data, a cache can satisfy a large fraction of its processor's memory requests, thereby reducing both the average memory latency and the processor's demand on the interprocessor communication network.

However, caches in a multiprocessing environment introduce the cache coherence problem. When multiple processors maintain locally cached copies of a unique shared-memory location, any local modification of the location can result in a globally inconsistent view of memory, violating the shared-memory abstraction. Cache-coherence protocols prevent this problem by maintaining a uniform state for each cached block of data. While it is possible to implement a cache coherence protocol with a multiprocessor-wide broadcast, such a mechanism negates the bandwidth reduction that makes caches attractive in the first place. Furthermore, in large-scale multiprocessors, broadcast mechanisms are either inefficient or prohibitively expensive to implement.

Is it possible to use caches to build an efficient shared-memory system for a large-scale multiprocessor? The answer to this question depends on finding a solution to the cache coherence problem that relies only on scalable hardware mechanisms.

#### 1.1 Cache Coherence for the Alewife Machine

This thesis describes the search for a cache coherence protocol for Alewife, a large-scale multiprocessor being built at MIT. Not only does the Alewife project provide concrete motivation for solving the cache coherence problem, but it also establishes fundamental constraints on potential solutions to the problem. Since the Alewife machine is intended to be both scalable and easily programmable, its memory system must conform to both of these goals:

First, the memory system's cache coherence protocol must be scalable. That is, the physical resources required to implement the cache coherence scheme must be cost-effective, and independent of the number of processors in the system. An optimal solution would require only a small, constant amount of overhead per processing node. Given such a solution, the physical size of the memory system grows as  $\Theta(N)$ , where N is the number of processors in the machine. More realistically, since the size of a processor identifier in a system grows as  $\Theta(\log N)$ , it is reasonable to expect the cache coherence overhead to grow logarithmically with the number of processors. This design decision requires a cache coherence protocol that transmits all memory transactions over a mesh network without a broadcast mechanism.

Second, to allow Alewife to be both scalable and easily programmable, not only must the interprocessor communication system exploit locality to minimize the latency needed to service processor requests, but it must also provide mechanisms for automatic locality management. Caches allow the system to automatically move data to processors, thereby increasing the locality of access within processing nodes, in a manner that is completely transparent to the user. Furthermore, by distributing the shared-memory modules to the processing nodes and by using a packet-switched mesh network to interconnect the nodes, the memory system allows the software to take

advantage of communication locality between processing elements.

The protocols considered for the Alewife machine solve the cache coherence problem in the absence of a broadcast mechanism. Each coherence scheme allocates a section of the multiprocessor's memory, called a directory, to store the locations of the cached copies of each data block. Instead of broadcasting the fact that a processor has modified a data location, the memory system sends an individual message to each cache that has a copy of the data. The protocol must also record the acknowledgment of each of these messages to ensure that the global view of memory is actually consistent. This message-based approach dramatically reduces the network bandwidth needed to enforce coherence.

In order to determine whether such protocols meet the requirements of Alewife, several different simulation techniques are used. First, a hybrid decoupled simulation methodology provides evidence that a cached-based shared-memory system is viable. Then, coupled simulations of the Alewife machine allow a complete analysis of both the implementation and the behavior of potential cache coherence schemes. In the end, the choice of a protocol is based on the complexity and the performance of each coherence scheme, as measured by memory overhead and processing speed for a range of benchmark applications.

#### 1.2 Cache Coherence as a General Problem

Although the Alewife project motivates the search for scalable solutions to the cache coherence problem, both the results and the methodology of the search are applicable to the more general task of designing large-scale shared-memory multiprocessors. This thesis contributes some of the first results for directory-based coherence protocols that are implemented and evaluated on memory systems with interconnection networks other than buses. The detailed implementation of various coherence schemes helps to isolate the protocol features that strongly effect the performance of shared memory from the components that have only a weak effect.

The results of the evaluation of different cache coherence protocols emphasizes

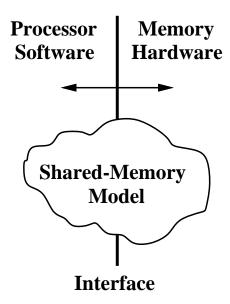

Figure 1-1: The implementation of a shared-memory model must be divided between the processor and the memory system.

the importance of the integrated systems approach. In the case of a shared-memory multiprocessor, the approach balances the size of a shared-memory system's hardware with the complexity of a multiprocessor's software by handling common events in hardware and exceptional situations in software. This philosophy helps to draw the line between the subset of the memory model that is implemented in hardware and the subset that is implemented in software. As depicted in Figure 1-1, the architectural problem of implementing a shared-memory system is solved by specifying the appropriate interface between the processor and the memory system.

The evaluation of coherence methods reveals a number of software optimizations that increase the performance of a cache-based memory system. Dividing the responsibility for implementing the memory model between hardware and software helps to mitigate the effects of widely-shared data on the performance of cache coherence schemes. In fact, the search for a coherence protocol culminates with the definition of the scalable LimitLESS directory protocol, which uses a combination of hardware and software methods to realize the performance of the best non-scalable directory protocol. Perhaps the largest contribution of the research lies in establishing the trade-offs between hardware and software that are necessary to achieve both scalability and

high performance in a large shared-memory multiprocessor.

#### 1.3 Organization of this Thesis

The rest of this thesis is organized as follows: Chapter 2 establishes the characteristics of the cache coherence problem by discussing previous attempts to solve the problem. Chapter 3 clarifies the constraints on coherence protocols for large-scale multiprocessors by describing the relevant features of the Alewife architecture. Chapter 3 also defines the LimitLESS protocol in the context of the Alewife machine. Chapter 4 describes the simulation techniques that are used to evaluate the protocols. Finally, Chapter 5 presents the results from the multiprocessor simulations and draws conclusions about the performance of large-scale shared-memory systems.

# Chapter 2

# Background

#### 2.1 Why Study Caches?

Multiprocessor caches promise to yield performance gains similar to the gains from caches in uniprocessor applications, despite increased implementation complexity. It is the promise of a high-bandwidth, low-latency path to memory that makes multiprocessor cache systems a useful and interesting topic of research. To understand the benefits and problems of using caches in machines with many processors, it is necessary to understand the place of caches in single processor systems.

#### 2.1.1 Single Processor Caches

A cache is a data storage repository that provides fast access to a subset of data from a larger, slower block of memory. Common examples of caches include memory buffers for disk accesses and translation lookaside buffers (TLB) for paging tables of virtual memory systems. In the context of a physical memory system, the term cache refers to a chunk of fast — low latency — memory (typically implemented as static random access memory, or SRAM) that provides a processor with a local subset of data from main memory (typically implemented as dynamic random access memory, or DRAM). The physical proximity of a cache to a processor permits a high-bandwidth data path between the two. Processor caches have been implemented in

applications from personal computers to supercomputers.

When a processor requests data from its cache, the data may already be located in the cache (a hit), or the cache may have to fetch the data from main memory (a miss). Uniprocessor caches work due to two principles of memory access patterns: temporal locality and spatial locality. Temporal locality refers to the fact that if a processor accesses a unit of memory (called a word), then it is likely to access the same word in the near future. Spatial locality refers to the fact that if a processor accesses a word of memory, then it is likely to access a nearby word in the future. A processor's cache capitalizes on temporal locality by retaining copies of words of memory that the processor accesses, and on spatial locality by fetching a block (a number of consecutive memory words) at once.

The actual performance of a cache is measured by the average memory access time,  $T_a$ , a metric that encapsulates the effects of both locality and the physical parameters of the cache.  $T_a = hT_h + mT_m$ , where h is the hit rate in the cache, m = 1 - h is the miss rate in the cache,  $T_h$  is the time required to service a hit in the cache, and  $T_m$  is the time required to service a miss in the cache. If the time to service a hit in the cache is the same as the processor cycle time, the average access time and miss access time can be normalized to the cycle time:  $T_a = h + mT_m$ , where  $T_a$  and  $T_m$  are given in terms of processor cycles. Perhaps a more intuitive metric of cache performance is the processor utilization, defined as the fraction of time that the processor is not waiting for memory and is therefore doing useful work. Processor utilization, U, is given by:

$$U = \frac{1}{1 + mT_m}$$

The cache design parameters that affect the hit rate and access times for a cache have been studied by simulating cache based memory systems on various memory access patterns. These access patterns may be generated by statistical methods or by traces of actual processor memory requests. The issues of cache implementation in uniprocessor applications have been exhaustively studied, and in 1982, Alan Jay Smith published a paper that is considered to be the authoritative work on the sub-

ject [41].

It is important to realize that given any caching scheme, it is always possible to write an application that "breaks" the scheme. Some programs simply do not exhibit the proper temporal or spatial locality to utilize a cache. However, the vast majority of uniprocessor programs profit from caches, and caching has proved to be a successful strategy for memory system design.

#### 2.1.2 Multiprocessor Caches

The argument for using caches in the implementation of a multiprocessor's shared-memory system is even more compelling than the argument for single processor memory systems. In multiprocessors with shared memory, cache-based memory systems automatically move data where it is needed. When a processor attempts to read or write a unit of data, the memory system fetches the data from a remote memory module into a cache that is located in the same physical node as the processor. Subsequent load and store accesses to the same data are satisfied within the local processing node. After the working-set of each processor migrates into its cache, the memory system can perform a large percentage of processor requests without communicating over the multiprocessor's interconnection network.

Satisfying most memory requests in a cache increases the performance of the system in two ways: First, since typical cache access times are an order of magnitude lower than interprocessor communication times, the memory access latency incurred by each processor is lower than in a system that does not cache data. Second, when most requests are performed within processing nodes, the absolute amount of traffic that the network must transport is lower than in a system without caches. For caches to be effective in multiprocessors, parallel programs must display processor locality, in addition to the usual temporal and spatial locality. *Processor locality* is defined as the tendency of a processor to repeatedly access a block of data before the block must be relinquished upon a request (typically a write) from another processor [4].

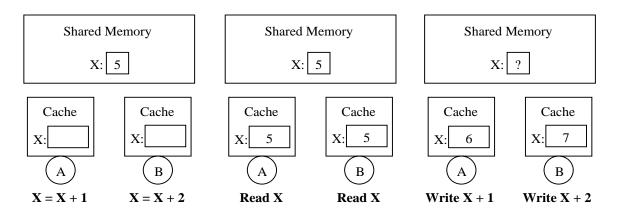

Figure 2-1: Illustration of the cache coherence problem.

#### 2.2 The Cache Coherence Problem

The fact that more than one processor can cache a single block of data leads to the cache coherence problem, which is usually explained by an example such as the one that follows: Suppose that processor A and processor B both try to add the integers 1 and 2, respectively, to the value stored in memory location X, which contains the integer 5. (See Figure 2-1.) Both processors cache copies of X, and add their respective values to the cached value. But what should be the final value stored in memory location X?

The answer to this question depends on the shared memory model that is specified for the multiprocessor containing A, B, and X. A programmer's intuition would say that one processor (either A or B) should see the original value (5), the other processor should see the intermediate value (6 or 7), and the final value should be the integer 8, since 5 + 1 + 2 = 5 + 2 + 1 = 8. Leslie Lamport [33] captured this programmer's intuition when he wrote that a multiprocessor's memory should obey the condition of sequential consistency:

"... the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program."

To guarantee sequential consistency (or any other shared-memory model) in a

cache-based memory system, all transactions between caches and shared-memory modules are conducted through a cache coherence protocol. A cache coherence protocol consists of the set of possible states in the caches, the states of the data in the main memory, and the messages that must be transported through the processor interconnect to keep memory consistent. In order to guarantee consistency, a coherence scheme must sometimes force caches to evict data. Processor locality is determined by the number of times that a processor accesses a cached block of data before the coherence protocol causes the block to be evicted. Dubois, Scheurich, and Briggs have described the various alternatives for maintaining cache coherence and have summarized the methods implemented to date [18, 19]. Archibald's doctoral dissertation [7] is a good reference on the implementation of a wide class of coherence protocols, although the paper by Yen, Yen, and Fu [45] is easier to find in the literature.

While sequential consistency presents a tractable memory model to programmers, it places strong constraints on the memory system. Enforcing sequential consistency requires caches to stall processor write requests to ensure that only one write request is pending at any given time. Otherwise, individual processors may observe write operations in different orders, leading to a violation of the memory model. Several memory system designers have identified less stringent memory models that allow write requests to be overlapped with other processor accesses to shared memory [1, 19, 21]. These weakly-ordered models permit the memory system to overlap certain memory transactions by forbidding certain kinds of data sharing semantics. For example, weakly-ordered systems do not guarantee the appropriate behavior in the scenario depicted by Figure 2-1, unless the two processors synchronize between accesses to location X. However, the ability to overlap a number of memory transactions allows a processor to tolerate the latency of access to shared memory. Weakly ordered systems also tend to improve performance by increasing processor locality.

The Alewife architecture takes a slightly different approach to the problem of shared-memory latency. As described in Chapter 3, Alewife's SPARCLE processor overlaps memory transactions by switching between threads of control — which are implemented as hardware contexts — when its cache needs to transmit a request to a

remote shared-memory module. Thus, the memory system can overlap one memory transaction per context, while still enforcing a sequentially consistent memory model for each thread of control. Since this research focuses on finding a cache coherence protocol for Alewife, only implementations of sequentially consistent shared-memory models are evaluated. Nevertheless, all of the general classes of protocols that are considered can be implemented to enforce either sequential consistency or weak ordering. Although the main thrust of this research attempts to use caches to minimize the remote latency through the use of caches, it also investigates the relative benefits of weak ordering and multiple contexts.

#### 2.2.1 Classes of Cache Coherence Protocols

The cache coherence problem has been solved adequately for multiprocessors with a small number of processors. Systems of up to about sixteen processors may be constructed by connecting each processor node (consisting of a processor, a cache, and a bus interface) and the memory modules (often distributed with the processor nodes) to a bus. Since each node transmits and receives all of its memory transactions via this common communication resource, any processor node can observe the memory transactions of all of the other nodes in the system. Protocols that take advantage of this technique of covert observation are called *snoopy* cache coherence protocols, because each processor node snoops on the bus transactions of the other nodes. Snoopy protocols have been extensively studied, and have been implemented in several systems [20, 22, 26, 27].

Unfortunately, the protocols used in small multiprocessing systems do not scale up to systems with large numbers of processors, due to physical constraints on the processor interconnect structure. Specifically, a bus simply does not have the bandwidth to support a large number of high-speed processors. Furthermore, transmission problems in a multidrop environment cause the latency of bus transactions to rise with the number of nodes connected to a bus. So, systems with large numbers of processing elements must use point-to-point interconnection networks. But replacing a bus with another type of interconnect removes the broadcast mechanism that is implicit in bus

operation. While it is possible to implement a broadcast as a part of a multiprocessor network, such a mechanism incurs a long latency or large hardware cost due to the necessity for receiving acknowledgments from every node in the system. The lack of a broadcast mechanism renders snoopy protocols infeasible for large multiprocessor designs.

Some methods for solving the cache coherence problem in large multiprocessors bypass the problem entirely. For example, the Denelcor HEP [25] avoids the use of caches by hiding memory access latency with fine grain multitasking. However, this system requires an interconnection network with a very high bandwidth.

The NYU Ultracomputer [23] and the IBM RP3 [39] use caches, but avoid the coherence problem by not caching shared data. Instead, caches are only allowed to store copies of private data, shared data that is read-only, and instructions, while accesses to shared data bypass the cache. These systems often try to overlap the latency of write requests to shared data by allowing multiple outstanding writes. When necessary, the multiprocessor software must enforce consistency by issuing fence instructions, which stall a processor until all of its previous shared memory requests have been satisfied. While the experimentation with reduced cache use has led to some interesting results in the relationship between program execution and software-based coherence mechanisms [40], the efforts in shared memory research have shifted towards systems that have hardware mechanisms to enforce cache coherence.

This shift has occurred partially due to the fact that, in practice, shared variables must be statically identified to use this coherence scheme. Software systems that can not use compiler or programmer analysis to differentiate between private and shared variables are precluded from using this scheme. Nonetheless, the software-based coherence method is not rejected out-of-hand and is compared with the other protocols for large-scale machines. In later analysis, this coherence method is designated by the acronym OCPD, which stands for *only cache private data*. To facilitate the comparison of this method with hardware-based coherence scheme, sequential consistency is ensured by an implicit fence operation after every reference to a shared variable.

Hardware-based cache coherence protocols that do not use broadcasts store the

locations of all cached copies of each block of shared data. This list of cached locations, whether organized as a table or a linked-list, is called a *directory*. There is a directory entry for each block of data containing a number of pointers to specify the locations of copies of the block. Each directory entry also contains a dirty bit to specify whether or not a unique cache has permission to write a given block of data.

#### 2.3 Directory-Based Cache Coherence Protocols

The different flavors of directory protocols that have been devised previously fall under three primary categories: full-map directories, limited directories, and chained directories. Full-map directories [9] store enough state associated with each block in global memory so that every cache in the system can simultaneously store a copy of any block of data. That is, each directory entry contains N pointers, where Nis the number of processors in the system. Such directories can be optimized to use a single bit pointer, and the directory can also be physically distributed along with main memory, to allow the directory to match the bandwidth of main memory. Due to bandwidth requirements, only distributed directory schemes are considered for Alewife. Limited directories [6] differ from full-map directories in that they have a fixed number of pointers per entry, regardless of the number of processors in the system. In order to avoid using a broadcast mechanism, limited directory schemes only permit a small, fixed number of copies of any given block to be cached simultaneously. Chained directories [24] emulate the full-map schemes by building each directory entry as a linked-list structure and by allocating one link to each cache in the list.

#### Full-Map Directories

Full-map protocols were proposed by Tang [42] and Censier and Feautrier [9]. The Censier and Feautrier protocol uses directory entries with one bit per processor and a dirty bit. Each bit represents the status of the block in the corresponding processor's cache (present or absent). If the dirty bit is set, then one and only one processor's bit

is set, and that processor has permission to write into the block. A cache maintains two bits of state per block: One bit indicates whether or not a block is valid; the other bit indicates whether or not a valid block may be written. The cache coherence protocol must keep the state bits in the memory directory and those in the caches consistent.

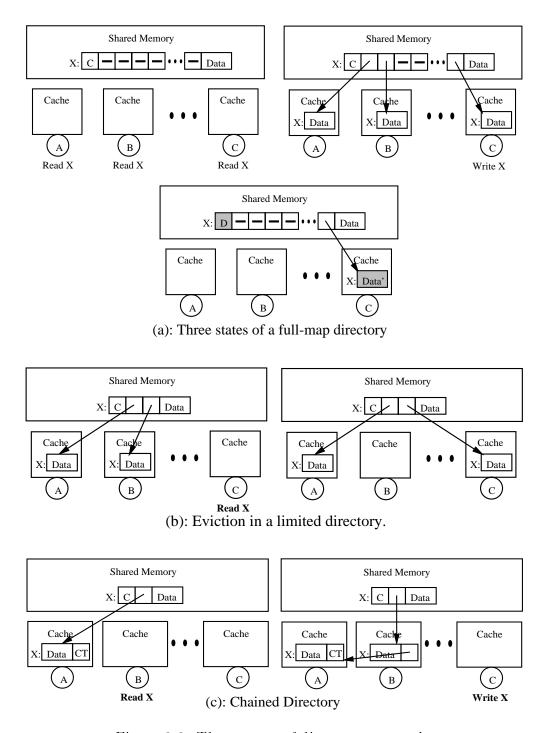

Figure 2-2a illustrates three different states of a full-map directory. In the first state, location X is absent from all of the caches in the system. The second state results from three caches (caches A, B, and C) requesting copies of location X: Three pointers (processor bits) are set in the entry to indicate the caches that have copies of the block of data. In the first two states, the dirty bit — on the left of the directory entry — is set to clean (C), to indicate that no processor has permission to write to the block of data. The third state results from cache C requesting write permission for the block. In this final state, the dirty bit is set to dirty (D), and there is a single pointer to the block of data in cache C.

It is worth examining the transition from the second to third states in more detail.

Once processor C issues the write to cache C, the following events transpire:

- 1. Cache C detects that the block containing location X is valid, but that the processor does not have permission to write to the block as indicated by the block's write-permission bit in the cache.

- 2. Cache C issues a write request to the memory module containing location X and stalls processor C.

- 3. The memory module issues invalidate requests to caches A and B.

- 4. Cache A and cache B receive the invalidate requests, set the appropriate bit to indicate that the block containing location X is invalid, and send acknowledgments back to the memory module.

- 5. The memory module receives the acknowledgments, sets the dirty bit, clears the pointers to caches A and B, and sends write permission to cache C.

Figure 2-2: Three types of directory protocols.

6. Cache C receives the write permission message, updates the state in the cache, and reactivates processor C.

Note that the memory module waits to receive the acknowledgments before allowing processor C to complete its write transaction. By waiting for acknowledgments, the protocol guarantees that the memory system ensures sequential consistency.

The full-map protocol provides a useful upper bound for the performance of directory-based cache coherence. However, it is not scalable with respect to memory overhead: Assume that the amount of distributed shared memory increases linearly with the number of processors N. Because the size of the directory entry that is associated with each block of memory is proportional to the number of processors, the memory consumed by the directory is proportional to the size of memory  $(\Theta(N))$ , multiplied by the size of the directory entry  $(\Theta(N))$ . Thus, the total memory overhead scales as the square of the number of processors  $(\Theta(N^2))$ .

#### Limited Directories

Limited directory protocols are designed to solve the directory size problem [6]. By restricting the number of simultaneously cached copies of any particular block of data, it is possible to limit the growth of the directory to a constant factor.

A directory protocol can be classified as  $Dir_iX$  using the notation from [6]. The symbol i stands for the number of pointers, and X is NB for a scheme with N0 B1 roadcast and B for one with B2 roadcast. A full-map scheme without broadcast is represented as  $Dir_NNB$ . A limited directory protocol that uses i < N pointers is denoted  $Dir_iNB$ . The limited directory protocol is similar to the full-map directory, except in the case when more than i caches request read copies of a particular block of data.

Figure 2-2b shows the situation when three caches request read copies in a memory system with a  $Dir_2NB$  protocol. In this case, the 2-pointer directory may be viewed as a 2-way set-associative cache of pointers to shared copies. When  $cache\ C$  requests a copy of  $location\ X$ , the memory module must invalidate the copy in either  $cache\ A$  or  $cache\ B$ . This process of pointer replacement is sometimes called eviction. Since the

directory acts as a set-associative cache, it must have a pointer replacement policy. The protocols evaluated in this study use a pseudorandom eviction policy that is easy to implement and requires no extra memory overhead. In Figure 2-2b, the pointer to cache B is replaced by the pointer to cache C.

Why might limited directories be successful? If a parallel program exhibits the worker-set property in the sense that in any given interval of time only a small subset of all the processors access a given memory word, then a limited directory is sufficient to capture this small "worker-set" of processors. It is important to recognize that in a properly written multiprocessor program, there can not be an overwhelming number of variables that are both widely-shared and frequently written. If a program utilizes such variables, then the amount of traffic needed to transmit the data associated with the variables would surely exhaust the bandwidth of the interconnection network, no matter what mechanism is used to ensure the shared-memory model.

Directory pointers in a  $Dir_iNB$  protocol encode binary processor identifiers, so each pointer requires  $i \log_2 N$  bits of memory, where N is the number of processors in the system. Given the same assumptions as for the full-map protocol, the memory overhead of limited directory schemes grows as  $\Theta(N \log N)$ . These protocols are considered scalable with respect to memory overhead because the resources required to implement them grow approximately linearly with the number of processors in the system.

$Dir_iB$  protocols allow more than i copies of each block of data to exist, but they resort to a broadcast mechanism when more than i cached copies of a block need to be invalidated. However, interconnection networks with point-to-point wires do not provide an efficient system-wide broadcast capability. In such networks, it is also difficult to determine the completion of a broadcast to ensure sequential consistency. While it is possible to limit some  $Dir_iB$  broadcasts to a subset of the system (see [6]), the evaluation of limited directories for Alewife is restricted to the  $Dir_iNB$  protocols.

#### Chained Directories

Chained directories, the third option for cache coherence schemes that do not utilize a broadcast mechanism, realize the scalability of limited directories without restricting the number of shared copies of data blocks [24]. This type of cache coherence scheme is called a *chained* scheme, because it keeps track of shared copies of data by maintaining a linked-list of directory pointers.

Two different chained directory schemes have been proposed. The simpler of the two schemes implements a singly-linked chain, which is best described by example (see Figure 2-2c.). Suppose there are no shared copies of location X. If processor A reads location X, the memory sends a copy to cache A, along with a chain termination (CT) pointer. The memory also keeps a pointer to cache A. Subsequently, when processor B reads location X, the memory sends a copy to cache B, along with the pointer to cache A. The memory then keeps a pointer to cache B. By repeating this step, all of the caches can store a copy of location X. If processor C writes to location X, it is necessary to send a data invalidation message down the chain. To ensure sequential consistency, processor C is denied write permission by the memory module until the processor with the chain termination pointer acknowledges the invalidation of the chain. Perhaps this scheme should be called a gossip protocol (as opposed to a snoopy protocol) because information is passed from individual to individual, rather than being spread by covert observation!

Chained directory protocols are complicated by the possibility of cache block replacement. Suppose that  $cache\ A_1$  through  $cache\ A_N$  all have copies of  $location\ X$ , and that  $location\ X$  and  $location\ Y$  map to the same (direct-mapped) cache line. If  $processor\ A_i$  reads  $location\ Y$ , it must first evict  $location\ X$  from its cache. In this situation, there are two possibilities: 1) Send a message down the chain to  $cache\ A_{i-1}$  with a pointer to  $cache\ A_{i+1}$  and splice  $A_i$  out of the chain, or 2) Invalidate  $location\ X$  in  $cache\ A_{i+1}$  through  $cache\ A_n$ .

Another solution to the replacement problem is to use a doubly-linked chain. This scheme maintains forward and backward chain pointers for each cached copy so that the protocol does not have to traverse the chain when there is a cache replacement.

The doubly-linked directory optimizes the replacement condition at the cost of a larger average message block size (due to the transmission of extra directory pointers), twice the pointer memory in the caches, and a more complex coherence protocol.

Although the chained protocols are more complex than the limited directory protocols, they are still scalable in terms of the amount of memory used for the directories. The pointer sizes grow as the logarithm of the number of processors, and the number of pointers per cache or memory block is independent of the number of processors.

#### 2.4 Qualitative Evaluation of the Protocols

The abundance of protocols in the literature might lead to the belief that the cache coherence problem has already been solved. However, each of the protocols described in this chapter have defects in terms of scalability or performance. While the full-map directory protocol allows unlimited data sharing, its hardware overhead becomes costly for systems with hundreds of processors. Limited directory protocols solve this problem, but they depend on the assumption that worker-set sizes for all memory locations are small. The simulations described in Chapters 4 and 5 show that it is possible to optimize software to reduce the sizes of worker-sets, thereby making limited directory protocols a viable coherence method. However, the performance of a shared-memory system based on a limited directory protocol is extremely sensitive to the extent that multiprocessor software can manage data sharing.

Chained directory protocols suffer from a more subtle problem. Although chained directories perform only slightly worse than full-map directories in simulations of systems with up to 256 processors, the scalability of this class of protocols may be hampered by the structure of the directory. Full-map and limited directory protocols can service processor write requests by transmitting multiple invalidations through the interconnection network at once. The latency of a write request is determined by the rate at which invalidations can be formatted by a memory module, transmitted by the network, and acknowledged by the caches. In contrast, chained directory protocols must perform invalidations in the sequence determined by the linked-list representa-

tion of directory entries. Since chained schemes do not benefit from the parallelism inherent in a multiprocessor, the latency of a write request depends strongly on the number of caches in the system. As in the case of limited directories, if worker-set sizes are small, then chained directories should work well even for large systems. However, the linked-list structure may cause extreme sensitivity to the worker-set sizes of individual variables.

As defined, the directory schemes rely on the software to improve performance by reducing the size of shared variables' worker-sets, but none of the protocols allow the software to assume a subset of the memory system's functionality. This restriction is reasonable for systems built with contemporary hardware technology. However, as processor computation speed increases relative to interprocessor communication latency, implementing cache coherence functionality in software will become more and more attractive. The next chapter describes the Alewife architecture and its support for a protocol that allows a more integrated approach to the cache coherence problem.

# Chapter 3

# Implementing Cache Coherence in Alewife

Since the Alewife project serves as the platform for the analysis of cache coherence protocols, it is important to understand how the the memory system interacts with the rest of the Alewife architecture. This chapter begins by summarizing relevant features of the Alewife multiprocessor, and then describes the implementation of its cache-based memory system. The description emphasizes the reasoning behind design decisions that affect the complexity and the performance of the shared-memory system, rather than the minutia of the implementation of the coherence protocols. As part of the discussion of cache coherence implementation, the specification of the LimitLESS protocol serves as a case study of applying the integrated systems approach to shared memory systems.

#### 3.1 Scalability and Programmability

The goal of the Alewife experiment is to demonstrate that a parallel computer system can be both scalable and easily programmable. For the purposes of this thesis, scalability implies that both the physical size of each processing node and the size of the wires that connect the processors are constant with respect to the total number of nodes in the system. This definition of scalability is the basis for the discussion in

Chapter 2 that analyzes coherence protocols in terms of their memory overhead.

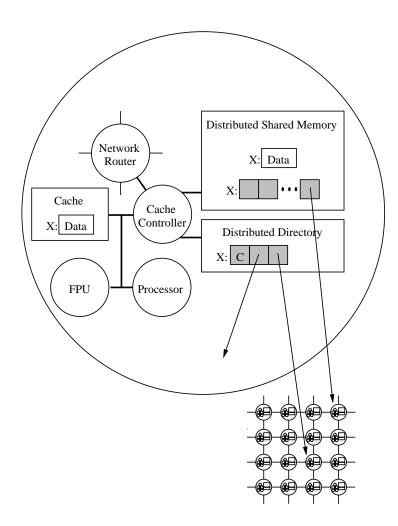

#### 3.1.1 The Alewife Processing Node

The Alewife multiprocessor, as depicted in Figure 3-1, is designed to be physically scalable. The system consists of a set of processing nodes that are connected by a mesh network. This type of network is scalable, because the interconnection wire lengths do not depend on the number of nodes in the system. Each node consists of a network router, a SPARCLE processor, a floating-point unit, a cache, a cachememory controller, and a portion of globally-shared memory. The shared memory is distributed to the processing nodes so that the system does not suffer from the bandwidth bottleneck of a single, monolithic memory. Figure 3-1 shows that the directory used by the cache coherence protocol is also distributed to the processing nodes. The description of the structures within the directory is deferred until later in this chapter.

Dividing the shared memory between the processing elements, rather than allocating it to specialized memory modules as in dance-hall architectures [23], has several benefits: First, the multiprocessor contains only one kind of node. This homogeneity makes the design of the system simpler, because only one type of circuit board needs to be fabricated. Second, the processor can access its local block of shared-memory without using the interconnection network. By allocating private data structures in local memory, Alewife's software reduces the network bandwidth that it requires. Third, the cache-memory controller, implemented as a single VLSI chip, incorporates all of the mechanisms needed to enforce cache coherence for both the cache and the local portion of shared memory. As is shown later in this chapter, the system also profits from the fact that each controller can interact closely with the local SPARCLE processor.

Assuming a scalable cache coherence protocol, the system's processing node is designed to be physically scalable. However, the Alewife architecture is intended to be scalable in a more powerful sense. As the system grows in terms of size, it should also scale in terms of performance. Although recent studies have attempted to

Figure 3-1: An Alewife processing element with a LimitLESS directory entry.

characterize scalable architectures [36], the concept of performance scalability does not have a widely-accepted definition. But from the point of view of the memory system, it is sufficient to recognize that the time needed for processors to communicate and synchronize with each other in a large system is the major obstacle to scalability. If this is the case, then a scalable system somehow must counteract the effects of interprocessor communication latency.

As described in [3], the Alewife architecture accomplishes the goal of scalability by exploiting communication locality:

A program running on a parallel machine displays communication locality if the probability of communication with various nodes decreases with physical distance.

Unfortunately, it is either difficult or tedious for programmers to have to create communication locality in a system. To achieve both scalability and programmability, the Alewife system presents the programmer with the abstraction of a monolithic, sequentially-consistent memory, while managing locality automatically. Alewife uses a combination of hardware and software techniques to *avoid* communication latency by exploiting locality and to *tolerate* latency when it is unavoidable. The memory system plays a key role in both of these strategies.

#### 3.1.2 Latency Avoidance

Processor caches provide the first line of defense against communication latency. A cache-based memory system automatically moves data into the processor nodes where it is needed. In doing so, the caches take advantage of the principles of temporal, spatial, and processor locality to increase the number of memory accesses that can be performed within a processing node, thereby enhancing the communication locality of multiprocessor programs.

However, the action of caches only enhances locality within processing nodes. The Alewife software implements mechanisms that increase the locality of communication between processing nodes. These software techniques partition multiprocess programs

into fragments, called tasks, and attempt to schedule these task in a way that enhances communication locality. Such methods include a partitioning mechanism that balances the size of tasks with the overhead of task creation, communication, and synchronization; scheduling heuristics that assign related tasks to processors that are physically near to one another; and compiler schemes that allocate tasks and their data to maximize locality. These methods are crucial to the scalability of the system as a whole, but they are beyond the scope of this thesis. The evaluation of coherence protocols concentrates on the interplay between software and hardware that is required to enhance locality within processing nodes.

## 3.1.3 Latency Tolerance

When the system can not avoid interprocessor communication, Alewife attempts to tolerate the latency by switching between hardware contexts on the SPARCLE processor, an implementation of the APRIL processor architecture for multiprocessing [5]. Each of the four hardware contexts on SPARCLE can contain the state of an executable task. When one task must be stalled due to internode communication caused by accessing a variable in a remote portion of memory, the SPARCLE processor rapidly switches to another task's context. (A context switch takes 11 cycles in the current implementation of the processor.) Thus, the context-switch allows the processor to overlap communication latency with useful execution of another part of the program. A cache coherence scheme must assure that the memory requests from each context are satisfied efficiently and correctly. Section 3.3.2 elaborates on the protocol features that are required to support multiple contexts.

## 3.2 Implementing Directory Protocols

Due to the reasons explained in Chapter 2, all of the potential cache coherence schemes for Alewife are directory-based protocols. For purposes of comparison, other types of protocols have been analyzed during the search for a protocol for Alewife; however, the main thrust of the memory system experimentation involves the simulation and measurement of several different directory-based protocols, including full-map, limited, and chained varieties. This analysis helps determine the relationship between the implementation of a protocol's directory structure and the performance of a shared-memory system.

The most dramatic differences in performance between protocols is caused by the structure of the directory. For applications that use variables with small worker-sets, all of the protocols perform similarly. On the other hand, applications with variables that are shared by many processors exhibit behavior that correlates with the type of directory used by the protocol. Except in anomalous situations, the full-map directory performs better than any other directory-based protocol. This observation should not be surprising, since the full-map protocol is also not scalable in terms of memory overhead. By committing enough resources to cache coherence, it is possible to achieve good performance.

Simulations show that limited directory protocols can perform as well as full-mapped directory protocols, subject to optimization of the software running on a system [11]. Although this result testifies to the fact that scalable cache coherence is possible, limited directories are extremely sensitive to the worker-sets of a program's variables. Chapter 5 examines a case-study of a multiprocessor application that — when properly modified — runs approximately as fast with a limited directory as with a full-map directory. However, when one variable in the program is widely shared, limited directory protocols cause more than a 100% increase in time needed to finish executing the application. This sensitivity to worker-set sizes varies with the program running on the system; but in general, the more variables that are shared among many processors, the worse limited directories perform.

Since chained directory protocols maintain pointers in a linked-list structure, they avoid the problems of limited directories by allowing an unlimited number of cached copies of any given variable. This class of directory protocols performs slightly worse than the full-map protocol, due to the latency of write transactions to shared variables. However, the fact that write latency differentiates the chained and full-map protocols even in 64 processor systems should cause some trepidation. As system

sizes grow, the effect of the linked-list structure becomes more pronounced.

## 3.2.1 The LimitLESS Directory Protocol

The LimitLESS directory protocol uses a different approach to solve the problem of finding a scalable cache coherence problem. As do limited directory protocols, the LimitLESS directory scheme capitalizes on the observation that only a few shared memory data types are widely shared among processors. Many shared data structures have a small worker-set, which is defined as the set of processors that concurrently read a memory location. The worker-set of a memory block corresponds to the number of active pointers it would have in a full-map directory entry. The observation that worker-sets are often small has led some memory-system designers to propose the use of a hardware cache of pointers to augment the limited-directory for a few widely-shared memory blocks [37]. However, when running properly optimized software, a directory entry overflow is an exceptional condition in the memory system. The LimitLESS protocol handles such "protocol exceptions" in software. This is the integrated systems approach — handling common cases in hardware and exceptional cases in software.

The LimitLESS scheme implements a small number of hardware pointers for each directory entry. If these pointers are not sufficient to store the locations of all of the cached copies of a given block of memory, then the memory module will interrupt the local processor. The processor will then emulate a full-map directory for the block of memory that caused the interrupt. The structure of the Alewife machine supports an efficient implementation of this memory system extension. Since each processing node in Alewife contains both a memory controller and a processor, it is a straightforward modification of the architecture to couple the responsibilities of these two functional units. This scheme is called LimitLESS, to indicate that it employs a Limited directory that is Locally Extended through Software Support. Figure 3-1, an enlarged view of a node in the Alewife machine, depicts a set of directory pointers that correspond to shared data block X, copies of which exist in several caches. In the figure, the software has extended the directory pointer array (which is shaded)

into local memory.

Since Alewife's SPARCLE processor is designed with a fast trap mechanism, the overhead of the LimitLESS interrupt is not prohibitive. The emulation of a full-map directory in software prevents the LimitLESS protocol from exhibiting the sensitivity to software optimization that is exhibited by limited directory schemes. But given current technology, the delay needed to emulate a full-map directory completely in software is significant. Consequently, the LimitLESS protocol supports small worker-sets of processors in its limited directory entries, implemented in hardware.

## 3.2.2 A Simple Model of the LimitLESS Protocol

Before discussing the details of the new coherence scheme, it is instructive to examine a simple model of the relationship between the performance of a full-map directory and the LimitLESS directory scheme. Let  $T_h$  be the average remote memory access latency for a full-map directory protocol.  $T_h$  encapsulates factors such as the delay in the cache and memory controllers, invalidation latencies, and network latency. Given the hardware protocol latency,  $T_h$ , it is possible to estimate the average remote memory access latency for the LimitLESS protocol with the formula:  $T_h + mT_s$ , where  $T_s$  (the software latency) is the average delay for the full-map directory emulation interrupt, and m is the fraction of memory accesses that overflow the small set of pointers implemented in hardware.

For example, simulations of a Weather Forecasting program running on 64 node Alewife memory system (see Chapter 5) indicate that  $T_h \approx 35$  cycles. If  $T_s = 100$  cycles, then remote accesses with the LimitLESS scheme will be 10% slower (on average) than with the full-map protocol when  $m \approx 3\%$ . Since the Weather program is, in fact, optimized such that 97% of accesses to remote data locations "hit" in the limited directory, the full-map emulation will cause a 10% delay in servicing requests for data.

LimitLESS directories are scalable, because their memory overhead grows as  $\Theta(N \log N)$ , and their performance approaches that of a full-map directory as system size increases. Although in a 64 processor machine,  $T_h$  and  $T_s$  are comparable, in

much larger systems the internode communication latency will be much larger than the processors' interrupt handling latency  $(T_h \gg T_s)$ . Furthermore, improving processor technology will make  $T_s$  even less significant. In such systems, the LimitLESS protocol will perform about as well as the full-map protocol, even if m=1. This approximation indicates that if both processor speeds and multiprocessor sizes increase, handling cache coherence completely in software will become a viable option. In fact, the LimitLESS protocol is the first step on the migration path towards interrupt-driven cache coherence. Other systems [14] have also experimented with handling cache misses entirely in software.

## 3.2.3 Background: Implementing a Full-Map Directory

Since the LimitLESS coherence scheme is a hybrid of the full-map and limited directory protocols, this new cache coherence scheme should be studied in the context of its predecessors. In the case of a full-map directory, one pointer for every cache in the multiprocessor is stored, along with the state of the associated memory block, in a single directory entry. The directory entry, illustrated in Figure 3-2, is physically located in the same node as the associated data. Since there is a one-to-one mapping between the caches and the pointers, the full-map protocol optimizes the size of the pointer array by storing just one bit per cache. A pointer-bit indicates whether or not the corresponding cache has a copy of the data. The implementation of the protocol allows a memory block to be listed in one of four states, which are listed in Table 3.1. These states are mirrored by the state of the block in the caches, also listed in Table 3.1. It is the responsibility of the protocol to keep the states of the memory and cache blocks coherent. For example, a block in the Read-Only state may be shared by a number of caches (as indicated by the pointer array). Each of these cached copies are marked with the Read-Only cache state to indicate that the local processor may only read the data in the block.

Before any processor modifies a block in an Invalid or Read-Only cache state, it first requests permission from the memory module that contains the data. At this point, the memory controller sends invalidations to each of the cached copies.

| State     | 1 | 2 | 3 | 4 |       | N |

|-----------|---|---|---|---|-------|---|

| Read-Only |   | X | X |   | • • • |   |

**Full-Map Directory Entry**

| State     | Cache ID | Cache ID | Cache ID | Cache ID |

|-----------|----------|----------|----------|----------|

| Read-Only | 12       | 10       | 09       | 15       |

### **Limited Directory Entry**

Figure 3-2: Full-map and limited directory entries. The full-map pointer array is optimized as a bit-vector. The limited directory entry has four pointers.

| Component | Name              | Meaning                                             |

|-----------|-------------------|-----------------------------------------------------|

| Memory    | Read-Only         | Caches have read-only copies of the data.           |

|           | Read-Write        | One cache has a read-write copy of the data.        |

|           | Read-Transaction  | Holding read request, update is in progress.        |

|           | Write-Transaction | Holding write request, invalidation is in progress. |

| Cache     | Invalid           | Cache block may not be read or written.             |

|           | Read-Only         | Cache block may be read, but not written.           |

|           | Read-Write        | Cache block may be read or written.                 |

Table 3.1: Directory states.

The caches then invalidate the copy (change the block's state from Read-Only to Invalid), and send an acknowledgment message back to the memory. The memory controller uses the Write-Transaction state to indicate that a memory location is awaiting acknowledgments, and sets a pointer to designate the cache that initiated the request. If the memory controller has a mechanism for counting the number of invalidations sent and the number of acknowledgments received, then the invalidations and acknowledgments may travel through the system's interconnection network in parallel. By allowing only one outstanding transaction per memory module, it is possible to avoid the extra memory overhead needed to store the Write-Transaction state and the acknowledgment counter for each directory entry. However, such a modification reduces the overall bandwidth of the memory system and exacerbates the effect of hot-spots, which may be caused by accesses to different variables that happen to be allocated in the same memory module. When the memory controller receives the appropriate number of acknowledgments, it changes the state of the block to Read-Write and sends a write permission message to the cache that originated the

transaction. In a sense, the cache "owns" the block until another cache requests access to the data.